PDP-11/05-S, 11/10-S system manual

1st Edition, October 1974 2nd Printing (Rev), January 1975

Copyright © 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

COMPUTER LAB

UNIBUS

**MASSBUS**

# **CONTENTS**

|           | rage                                                 |

|-----------|------------------------------------------------------|

| CHAPTER 1 | INTRODUCTION                                         |

| 1.1       | SCOPE                                                |

| 1.2       | SYSTEM COMPONENTS                                    |

| 1.2.1     | BA11-K Mounting Box                                  |

| 1.2.2     | Backplane                                            |

| 1.2.3     | KD11-B Processor                                     |

| 1.2.4     | KY11-J Programmer's Console                          |

| 1.2.5     | MM11-U Core Memory System                            |

| 1.2.6     | Unibus                                               |

| 1.3       | REFERENCE DOCUMENTS                                  |

| 1.4       | REFERENCE DRAWINGS                                   |

| CHAPTER 2 | INSTALLATION                                         |

| 2.1       | SCOPE                                                |

| 2.2       | ENVIRONMENTAL REQUIREMENTS                           |

| 2.2.1     | Humidity and Temperature                             |

| 2.2.2     | Air Conditioning                                     |

| 2.2.3     | Special Mounting Conditions                          |

| 2.2.4     | Static Electricity                                   |

| 2.3       | ELECTRICAL REQUIREMENTS                              |

| 2.4       | INSTALLATION PROCEDURES                              |

| 2.4.1     | Unpacking                                            |

| 2.4.2     | Inspection                                           |

| 2.4.3     | Cabinet and Slide Mounting Specifications            |

| 2.4.4     | Installation of LA36 DECwriter as an SCL Device      |

| 2.4.5     | Initial Power Turn-On                                |

| 2.5       | INSTALLATION CERTIFICATION                           |

| CHAPTER 3 | SYSTEM OPERATION                                     |

| 3.1       | SCOPE                                                |

| 3.2       | KY11-J PROGRAMMER'S CONSOLE                          |

| 3.2.1     | Console Power Key Switch                             |

| 3.2.2     | Function Switches                                    |

| 3.2.3     | ADDRESS/DATA Switches                                |

| 3.2.4     | Console Indicators                                   |

| 3.3       | CONSOLE OPERATION                                    |

| 3.3.1     | Load Address Switch                                  |

| 3.3.2     | Examine Switch                                       |

| 3.3.3     | Deposit Switch                                       |

| 3.3.4     | ENABLE/HALT Switch                                   |

| 3.3.5     | START Switch                                         |

| 3.3.6     | Continue Switch                                      |

| 3.4       | UNCONDITIONAL COMPUTER AND UNIBUS INITIALIZATION 3-6 |

| 3.5       | BASIC OPERATION                                      |

| 3.5.1     | Power On                                             |

| 3.5.2     | Basic Console Control                                |

| 3.5.2.1   | ENABLE/HALT Switch                                   |

| 3522      | Loading Data Manually 3-6                            |

# CONTENTS (Cont)

|                    |                                             | Page           |

|--------------------|---------------------------------------------|----------------|

| 3.5.3              | Manual Program Loading (Bootstrap Loader)   | . 3-7          |

| 3.5.4              | Automatic Program Loading                   | . 3-12         |

| 3.5.5              | Memory Dumps                                | . 3-14         |

| 3.5.5.1            | Operating Procedures                        | . 3-14         |

| 3.5.5.2            | Output Formats                              | . 3-15         |

| 3.5.5.3            | Storage Maps                                | . 3-15         |

| 3.5.6              | Running Programs                            | . 3-15         |

| 3.6                | BASIC PROGRAMMING                           | . 3-17         |

| CHAPTER 4          | INSTRUCTION SET                             |                |

| 4.1                | SCOPE                                       | 4 1            |

| 4.2                | ADDRESSING MODES                            |                |

| 4.2.1              | Introduction                                |                |

| 4.2.2              | Instruction Timing                          |                |

| 4.3                |                                             |                |

| 4.4                | PDP-11/05/10-S INSTRUCTIONS                 | . 4-2          |

| 4.4                | INSTRUCTION SET DIFFERENCES                 | . 4-2          |

| CHAPTER 5          | POWER SYSTEM                                |                |

| 5.1                | SCOPE                                       | 5-1            |

| 5.2                | H765 POWER SUPPLY                           |                |

| 5.3                | POWER SYSTEM                                | . 5-1<br>5-1   |

| 5.3.1              | Power Flow                                  |                |

| 5.4                | VOLTAGE REGULATOR OUTPUT SPECIFICATIONS     | . 5-1<br>. 5-2 |

| CHAPTER 6          | SYSTEM EXPANSION                            |                |

| 6.1                | SCOPE                                       |                |

| 6.2                | TYPES OF SYSTEM EXPANSION                   | . 6-1          |

| 6.3                | SPC INSTALLATION                            | . 6-1          |

| 6.4                | SPC INSTALLATION                            | . 6-2          |

| 6.5                | SYSTEM UNIT (SU) INSTALLATION               | . 6-2          |

| 0.5                | EXPANSION BOX INSTALLATION                  | . 6-2          |

| CHAPTER 7          | GENERAL MAINTENANCE                         |                |

| 7.1                | SCOPE                                       | . 7-1          |

| 7.2                | MAINTENANCE PHILOSOPHY                      | . 7-1          |

| 7.2.1              | Knowledge of Hardware Operation             |                |

| 7.2.2              | Detection and Isolation of Error Conditions |                |

| 7.2.3              | Means of Repairing Error Conditions         |                |

| 7.3                | MAINTENANCE EQUIPMENT REQUIRED              |                |

| 7.4                | PREVENTIVE MAINTENANCE                      |                |

| 7.4.1              | Physical Checks                             |                |

| 7.4.2              | Electrical Checks and Adjustments           |                |

| 7.4.2.1            |                                             |                |

| 7.4.2.1<br>7.4.2.2 | DC Voltage Checks                           | 7-4            |

| 7.4.2.2<br>7.4.2.3 | Processor Clock Adjustment Check            | 7-4            |

|                    | SCL Clock Adjustment Check                  | 7-4            |

| 7.5                | TROUBLESHOOTING PROCEDURES                  |                |

| 7.5.1              | Initial Investigation                       |                |

| 7.5.2              | Preliminary Check                           | 76             |

# CONTENTS (Cont)

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                                                      |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 7.5.3<br>7.5.4<br>7.6<br>7.6.1<br>7.7<br>7.7.1                                          | Run System Diagnostics Run Device Diagnostics  DIAGNOSTIC PROGRAMS General Description  KM11 MAINTENANCE MODULES Use of the KM11 Maintenance Modules  USE OF MODULE EXTENDERS                                                                                                                                                                                                                                                                                                                                                                                 | . 7-7<br>. 7-7<br>. 7-7<br>. 7-9<br>. 7-12                                                                |

| APPENDIX A                                                                              | CABLE CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |

| A.1<br>A.2<br>A.3<br>A.4                                                                | INTRODUCTION  SERIAL COMMUNICATIONS LINE INTERFACE  CONSOLE CABLE  UNIBUS CABLE/JUMPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . A-1<br>. A-1                                                                                            |

|                                                                                         | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |

| Figure No.                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                      |

| 1-1<br>1-2<br>1-3<br>1-4<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>3-1<br>3-2<br>3-3 | Relationship of Functional Components to Unibus and Internal Bus PDP-11/05/10-S Module Utilization Computer Backplane Connector and Pin Designations Module Contact Designations PDP-11/05/10-S Connectors 861-B, C Power Controller Connectors Computer Packaging PDP-11/05/10-S and BA11-K Mounting Box Cabinet Mounting Specification Accuride Slide Mounting Specification Chassis-Trak Slide Mounting Specification PDP-11/05/10 Programmer's Console Flowchart of Procedure for Loading and Running Programs Loading and Verifying the Bootstrap Loader | . 1-3<br>. 1-4<br>. 1-5<br>. 2-2<br>. 2-3<br>. 2-5<br>. 2-6<br>. 2-7<br>. 2-8<br>. 3-1<br>. 3-9<br>. 3-11 |

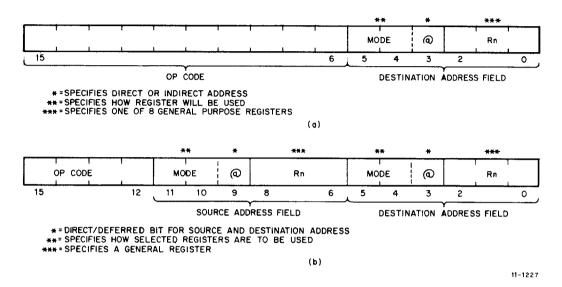

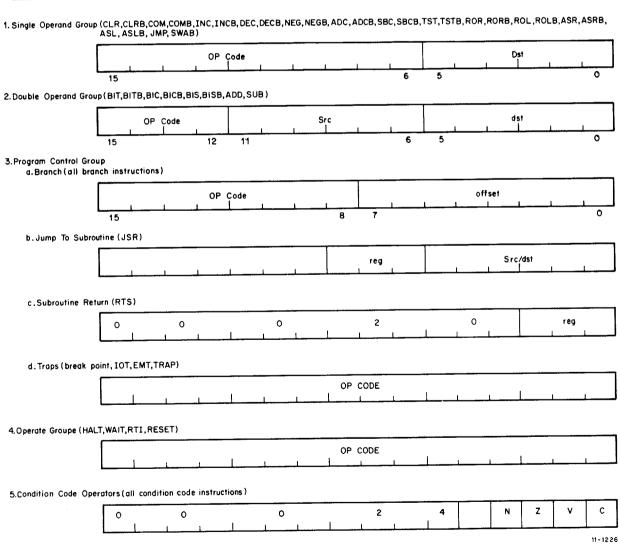

| 3-4<br>3-5<br>4-1                                                                       | Absolute Format  Bootstrap Format  Addressing Mode Instruction Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 3-16<br>. 4-2                                                                                           |

| 4-2<br>5-1<br>5-2<br>5-3<br>7-1                                                         | PDP-11 Instruction Formats Physical Layout of H765 Power Supply Power System Functional Block Diagram Power Distribution Board KM11 Maintenance Module Overlays                                                                                                                                                                                                                                                                                                                                                                                               | . 4-18<br>. 5-2<br>. 5-3<br>. 5-4<br>. 7-10                                                               |

| A-1                                                                                     | SCL Cable 70-08360                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . A-3                                                                                                     |

# **TABLES**

| Table No. | Title                                                      |              |  |  |  |  |

|-----------|------------------------------------------------------------|--------------|--|--|--|--|

| 1-1       | Reference Manuals                                          | 1.8          |  |  |  |  |

| 2-1       | 861-B, C Power Controller Primary Power Receptacles        | 2.3          |  |  |  |  |

| 2-2       | No Load Voltage Verification                               | 2.9          |  |  |  |  |

| 3-1       | Significance of ADDRESS/DATA Indicators                    | 3-3          |  |  |  |  |

| 3-2       | Program Identification Codes                               | 3-8          |  |  |  |  |

| 3-3       | Bootstrap Loader                                           | 3-10         |  |  |  |  |

| 3-4       | Binary Tape Load Selection (using Absolute Loader)         | 3-13         |  |  |  |  |

| 4-1       | Addressing Modes                                           | 4.3          |  |  |  |  |

| 4-2       | Addressing Times                                           | 4-4          |  |  |  |  |

| 4-3       | Single Operand Instructions                                | 4-5          |  |  |  |  |

| 4-4       | Double Operand Instructions                                | 4.9          |  |  |  |  |

| 4-5       | Program Control Instructions                               | 4.12         |  |  |  |  |

| 4-6       | Operate Group Instructions                                 | 4-17         |  |  |  |  |

| 4-7       | Condition Code Operators                                   | 4-18         |  |  |  |  |

| 4-8       | Table of Programming Differences                           | 4-19         |  |  |  |  |

| 5-1       | Regulator Output Specifications                            | 5-5          |  |  |  |  |

| 6-1       | SU Installation Requirements                               | 6-2          |  |  |  |  |

| 6-2       | Expander Box Installation Requirements                     | 6-3          |  |  |  |  |

| 7-1       | Maintenance Equipment Required                             | 7-3          |  |  |  |  |

| 7-2       | DC Voltage Checks                                          | . 7-3<br>7-4 |  |  |  |  |

| 7-3       | Baud Selection                                             | 7.5          |  |  |  |  |

| 7-4       | PDP-11/05/10 Diagnostic Programs                           | 7.9          |  |  |  |  |

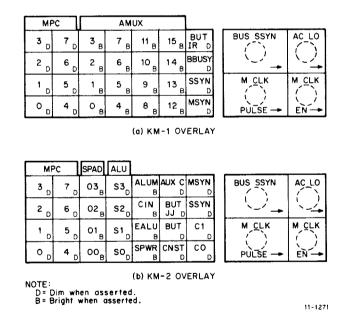

| 7-5       | KM-1 and KM-2 Overlay Designations                         | 711          |  |  |  |  |

| A-1       | SCL Interface Pin and Signal Designations                  | . /-11       |  |  |  |  |

| A-2       | BC08R-03 Console Cable Pin and Signal Designations         | . A-2        |  |  |  |  |

| A-3       | Unibus BC11A Cable/M920 Jumper Pin and Signal Designations | . A.4        |  |  |  |  |

|           |                                                            | . A.∙J       |  |  |  |  |

PDP-11/05-S, 11/10-S SYSTEM MANUAL

,

...

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual provides a general introduction to the PDP-11/05/10-S computer, including sections on installation, operation, the instruction set, options, equipment mounting, power, and maintenance, supplemented with references to other manuals in the PDP-11 series for detailed explanations.

The PDP-11/05/10-S series manuals provide the user with the theory of operation necessary to understand, operate, and maintain the PDP-11/05/10-S System. These manuals and the associated engineering drawings are discussed in Paragraph 1.3. The associated drawings are separate volumes documented by their Drawing Directory number. The manuals and drawings combine to form a complete documentation package.

The level of discussion in each manual assumes that the reader is familiar with basic digital computer theory. The maintenance philosophy presents information about normal system operation and enables the user to recognize trouble symptoms and take necessary corrective action. Each individual manual contains theory of operation, diagrams, and maintenance techniques.

This chapter lists the basic computer components (Paragraph 1.2) with a brief functional description and references applicable documents (Paragraph 1.3) and engineering drawings (Paragraph 1.4).

# 1.2 SYSTEM COMPONENTS

The PDP-11/05-S and the PDP-11/10-S are electrically the same. Digital Equipment Corporation (DEC) offers the PDP-11/05 for the Original Equipment Manufacturer (OEM). As such, it is sold in those configurations and with those services that are convenient for the OEM. The PDP-11/10 is offered for the End User and is sold in configurations that optimize its use with our small system software. More services and software are included with the PDP-11/10 for the End User.

The PDP-11/05-S and the PDP-11/10-S basic system incorporates the following major components:

- BA11-K Mounting Box

- 11/05/10 Backplane

- KD11-B Processor

- KY11-J Programmer's Console

- MM11-U Core Memory System

- Unibus

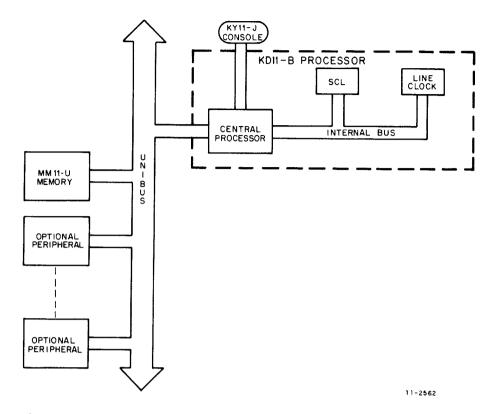

Figure 1-1 illustrates the relationship of the major functional components to the Unibus and the processor's internal bus.

Figure 1-1 Relationship of Functional Components to Unibus and Internal Bus

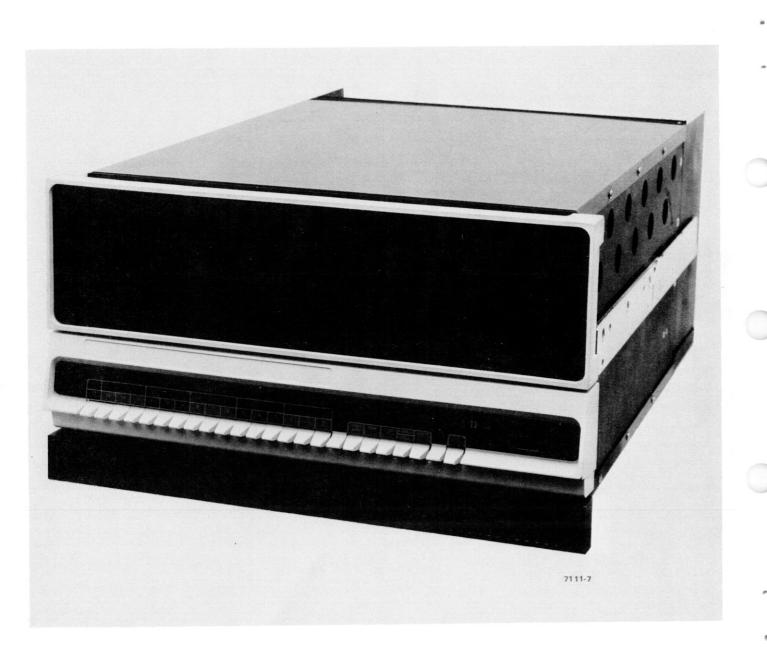

# 1.2.1 BA11-K Mounting Box

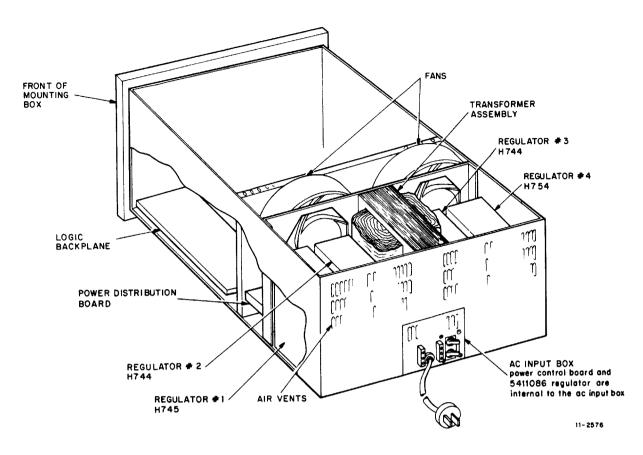

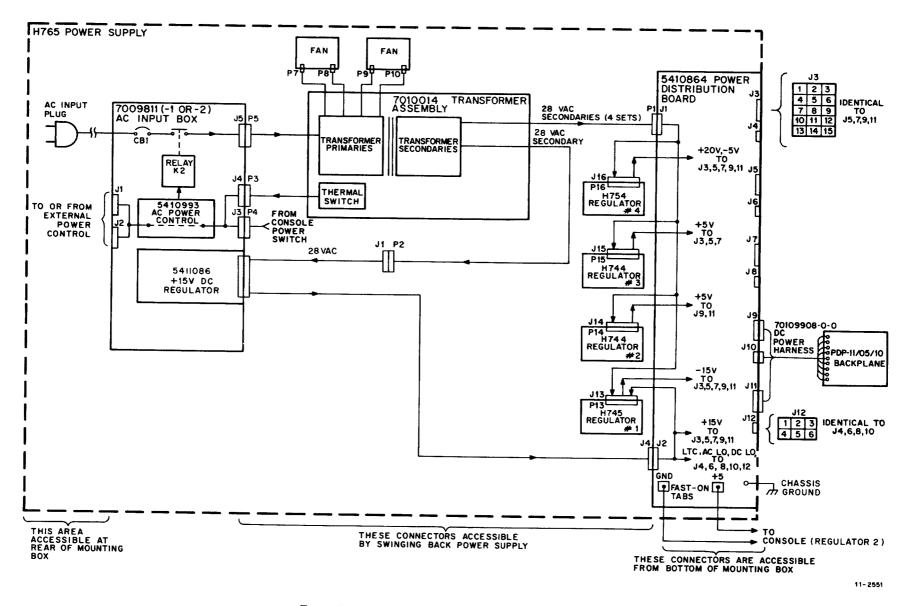

The BA11-K Mounting Box is used to house and supply power to the PDP-11/05-S and 11/10-S computer. Additional power capacity is available to supply power to options installed within the mounting box. In addition to voltages, the power supply within the BA11-K Mounting Box provides three logic signals (LTC L, AC LO L, and DC LO L) which are used within the processor and memory, and may be used by 11-family expansion systems. The H765 Power Supply within the BA11-K Mounting Box interfaces to the logic backplane(s) via the power distribution board (DEC Part No. 5410864). The mounting box and its power system are described in detail in the BA11-K Mounting Box Maintenance Manual.

H765 Power Supply – The H765 Power Supply contains a transformer assembly, an ac input box, fans, five regulators, and a power distribution board. The ac input box matches the H765 Power Supply to the available line voltage. A type 7009811-1 input box is used for 115 Vac. A type 7009811-2 input box is used for 230 Vac. The five regulators supply dc voltages via the power distribution board, to the backplanes mounted in the BA11-K. The power supply is controlled by the console power key switch via a remote control cable. The cable is run through the right hand side panel of the mounting box and plugs into one of four remote power control cable connectors (J3) on the power supply.

# 1.2.2 Backplane

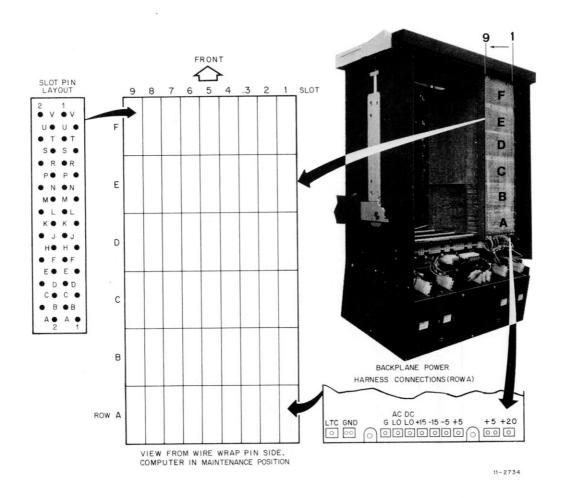

The backplane is the connector assembly into which the computer modules are plugged. It provides the signal and power routing among the logic modules that make up the PDP-11/05/10-S. The backplane contains nine slots which are utilized as illustrated in Figure 1-2. There are several slots that are prewired and dedicated for options (Small Peripheral Controllers, Serial Communication Line Connector Module M9970, and KM11-A and KM11-B Maintenance Modules). Power is brought to the backplane by a harness that plugs into the power distribution board of the H765 Power Supply. Power within the backplane is routed via the etch, while signal routing is implemented via the wire-wrap.

SLOT 6 5 KM11-A&B MAINTENANCE MODULE SECTION M930 UNIBUS TERMINATOR\*\* CONNECTOR MODULE M930 UNIBUS TERMINATOR **OR M997** KM11-A & B MAINTENANCE MODULE M9970 В H217-D MEMORY STACK MODULE M7260 CPU DATA PATHS MODULE SENSE/INHIBIT MODULE M7261 CPU CONTROL MODULE. 3235 X-Y DRIVE MODULE M8293 MEMORY CONTROL MODULE SLOT\* SPC SLOT\* SPC SLOT\* Ε If small peripheral controller is not installed, a G727 Grant Card is inserted in Section D MODULE SIDE OF BACKPLANE FRONT 11-2577

Figure 1-2 PDP-11/05/10-S Module Utilization

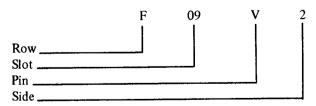

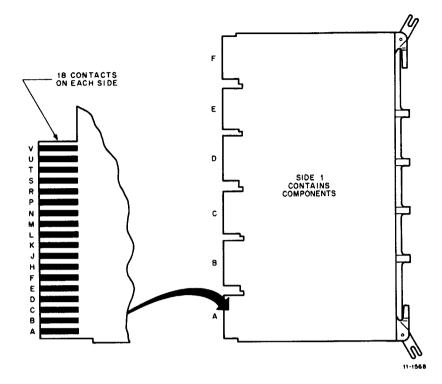

Figure 1-3 shows the backplane pin layout. The slots are numbered 1 through 9 and the rows are lettered A through F. Each row is pinned to accommodate a single-height, double-sided module edge-connector. The backplane accepts single, double, quad, and hex modules. A backplane pin is identified as follows:

Module contact designations are shown in Figure 1-4.

Figure 1-3 Computer Backplane Connector and Pin Designations

# 1.2.3 KD11-B Processor

The processor comprises the M7260 Data Path Module and the M7261 Control Logic and Microprogram Module. All the processor functional components are contained on these modules. The M7260 Data Path Module contains: data path logic, processor status word logic, auxiliary arithmetic logic unit control, instruction register and decoding logic, and serial communications line (SCL) interface. The M7261 Control Logic and Microprogram Module contains: internal address detecting logic, stack control logic, Unibus control logic, priority arbitration logic, Unibus drivers and receivers, microbranch logic, microprogram counter, control store logic, power fail logic, line clock, and processor clock.

The serial communications line interface is directly connected to the desired serial communications device. It can operate at speeds of 110-2400 baud and is program compatible with the KL11 Teletype Control Interface option.

The line time clock allows the program to measure time by sensing the LTC 50 Hz or 60 Hz ac line frequency signal from the power supply. This clock is program compatible with the KW11-L Line Time Clock option.

The line time clock and the serial communications line interface are not connected to the Unibus; they use an internal bus and can be addressed *only* by the processor and the console.

# Figure 1-4 Module Contact Designations

NOTES:

1

Side 1 is component side

Each side contains

A complete module contact designation contains a connector letter prefix,

18 contacts that are designated A-V (omitting G,I,O,Q,W,X,Y,Z)

contact letter, and side suffix number. for example: AD2

The KD11-B Processor decodes instructions; accepts, modifies and outputs data; performs arithmetic and logic operations; and controls allocation of the Unibus among external devices. The processor contains sixteen hardware registers, eight of which are programmable. Two of the eight programmable registers are specifically used for processor operation: a Program Counter (PC) and Stack Pointer (SP); while the remaining six serve as arithmetic accumulators, index register, and auto increment and auto decrement registers.

Four of the eight non-programmable registers are used for storage of a variety of functions including: source and destination data, the last interrupt vector address and load address storage. The remaining four are not used.

Because of the flexibility of hardware registers, address modes, instruction set, and DMA, PDP-11/05/10-S programs may be written in directly relocatable codes. The processor also includes a full complement of instructions that manipulate byte operands, including provisions for byte swapping.

Seven of the eight internal programmable registers (R0-R6) can be used to build last-in, first-out stacks. One register (R6) serves as a processor (or machine) Stack Pointer for automatic stacking. This stack handling capability permits save and restore of the Program Counter and Processor Status word in conjunction with subroutine calls and interrupts. This feature allows true re-entrant codes and automatic nesting of subroutines.

The Unibus is used by the processor and all peripheral devices; therefore there must be a priority structure to determine which device becomes bus master. A device generally requests use of the bus for one of two reasons: to make a nonprocessor transfer of data directly to or from memory, or to interrupt program execution and force the processor to branch to an interrupt service routine. An NPR is granted by the processor at the end of bus cycles and allows device-to-device data transfers without processor intervention. A BR is granted by the processor at the end of an instruction and allows the device to interrupt the current processor task.

The processor recognizes four levels of hardware BRs, with each major level containing sublevels. Many devices can be attached on each major level with the device that is electrically closest to the processor given priority over other devices on the same priority level. The priority level of the processor itself is programmable within the hardware levels; therefore, a running program can select the priority level of permissible interrupts.

Additional speed and power are added to the interrupt structure through the use of a fully vectored interrupt scheme. With vectored interrupts the device identifies itself and a unique interrupt service routine is automatically selected by the processor. This eliminates device polling and permits nesting of device service routines. The device interrupt priority and service routine priority are independent to allow dynamic adjustment of system behavior in response to real-time conditions.

Because of the 16-bit word length of the PDP-11/05/10-S, 32K words of address space can be referenced. Of these 32K words, the uppermost 4K words are reserved to reference I/O device registers and certain hardware registers within the processor. The remaining 28K words of address space are used to reference core memory. Although the word length of the 11/05/10 is 16 bits, the Unibus addresses generated by the KD11-B Processor contain 18-bits. All address references to the uppermost 4K words of 16-bit address space (160000–177777) are converted to full 18-bit references with bits 16 and 17 always set to 1. Thus, a 16-bit reference to address 173224<sub>8</sub> is automatically converted to a full 18-bit I/O device register address of 773224<sub>8</sub>. This allows all I/O device registers to maintain addresses in the range 760000 to 777777 in all PDP-11 systems and provides software compatibility among the computers in the PDP-11 line.

More detailed information is provided in the KD11-B Processor Maintenance Manual.

# 1.2.4 KY11-J Programmer's Console

The KY11-J Programmer's Console provides the programmer with a direct system interface and allows the user to start, stop, load, modify, examine, step, or continue a program. Console displays indicate processor operation and the contents of register and memory addresses. The console is mounted as the front panel of the BA11-K mounting box and is connected to the processor by a cable.

A detailed description of the programmer's console operating controls and indicators can be found in Chapter 3. The theory of operation of the console and its interaction with the KD11-B Processor is described in the KD11-B Processor Maintenance Manual.

# 1.2.5 MM11-U Core Memory System

Standard with the PDP-11/05/10-S is the MM11-U Core Memory. The MM11-U Core Memory is a read/write, random access, coincident current, magnetic core type memory with a cycle time of 1000 ns and a Unibus access time of 425 ns. The memory is organized in a 3D, 3-wire planar configuration providing 16,384 (16K) 16-bit words that are both word and byte addressable. Each 16-bit word contains two 8-bit bytes identified as the high-order byte (bits 15:08) and the low-order byte (bits 07:00). Each byte is addressable and has its own address location. Low bytes are always even numbered and high bytes are odd numbered. Full words are addressed at even-numbered locations only. When a full word is addressed, the high byte is automatically included. For example, the 16K memory has 16,384 words, or 32,768 bytes; therefore, 32,768 locations are assigned (addresses 000000 to 077777). Address 000000 is the first low byte, address 000001 is the first high byte, 000002 is the second low byte, 000003 is the second high byte, etc.

The MM11-U consists of four modules:

M8293 Memory Control Module – This quad-height module interfaces with the control and address lines of the Unibus and contains memory address latches, device selection, and read/write inhibit logic.

G114 Sense Inhibit Module – This hex-height module interfaces with the data lines of the Unibus and contains a data register, timing buffers, inhibit drivers, sense amplifiers, and threshold circuit.

G235 X/Y Driver - This hex-height module contains address decoders and X and Y drivers and switches.

H217D Stack Module — This hex-height module contains the ferrite core array and X-Y diode matrices. The ferrite core array consists of 16 mats, each containing 16,384 ferrite cores in a 128 by 128 planar array. Each mat represents a single bit position of a word. Each ferrite core can assume a stable magnetic state corresponding to either a binary 1 or binary 0. Even if power is removed from the core, the core retains its state until changed by appropriate control signals.

More detailed information on the MM11-U Core Memory may be found in the MM11-U/UP Core Memory System Maintenance Manual (DEC-11-HMFMA-B-D).

#### 1.2.6 Unibus

The Unibus provides high-speed communication between system components. The Unibus, with bidirectional data, address, and control lines, allows data transfers between all units on the bus with control of the bus an important factor in these transfers. The fixed repertoire of bus operations is flexible enough for speed and design economy, yet provides a fixed specification for interfaces. The asynchronous nature of these operations also eases design and operation. The repertoire of bus operations is:

Data Operations - DATa In (DATI), DATa In Pause (DATIP), DATa Out (DATO), DATa Out Byte (DATOB)

Control Operations – Bus Request (BR), INTerRupt (INTR), Non-Processor Request (NPR)

Full 16-bit words or 8-bit bytes of information can be transferred on the bus between the master and slave. The DATI, DATIP operations transfer data into the master; the DATO, DATOB operations transfer data out of the master. When a device is capable of becoming bus master and requests use of the bus, it is for one of two purposes: to make a Direct Memory Access (DMA) transfer of data directly to, or from, another device or memory without processor intervention; or to INTeRrupt (INTR) program execution and force the processor to branch to a specific address where an interrupt service routine is located.

Bus control is obtained under a Non-Processor Request (NPR) for the DMA, or under a Bus Request (BR) for an INTR. A device can perform a DMA after acquiring bus control via a BR.

Requests for the bus can be made at any time on the BR and NPR lines. Transfer of bus control from one device to another is made by the processor priority arbitration logic, which grants control of the bus to the device having the highest priority. NPR's are accorded higher priority than BR's. The NPR's are serviced before and immediately after Unibus data cycles, in addition to specific times during WAIT or TRAP sequences. The BR's are serviced upon completion of the current instruction if the requesting priority exceeds that of the processor.

The PDP-11/05/10-S processor has a special role in bus control operations as it performs the priority arbitration to select the next bus master.

The Unibus is terminated at both ends with a M930 Unibus Terminator module. To carry the Unibus from one system unit to an adjacent one, M920 Unibus Jumper modules are utilized; all 56 Unibus signals plus 17 grounds are carried by this one module. To connect system units in different mounting boxes, or to connect a peripheral device removed from the mounting box, a 120-conductor Flexprint cable is used.

A complete description of the Unibus, including specifications, is presented in the PDP-11 Peripherals Handbook.

# 1.3 REFERENCE DOCUMENTS

Table 1-1 lists the maintenance manuals and engineering drawings for the various components supplied as part of the basic PDP-11/05/10-S system and several reference manuals which provide essential information pertaining to all PDP-11 systems. Documentation for specific peripherals and options are *not* listed in the table. When peripherals and options are included in the PDP-11 system, the appropriate manuals are supplied with the system.

Table 1-1 Reference Manuals

| Title                                                                                                                                                                                                                                  | Document Number                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| PDP-11/05-S, 11/10-S Engineering Drawings KD11-B Processor Maintenance Manual MF11-U/UP Core Memory System Maintenance Manual BA11-K Mounting Box Maintenance Manual PDP-11/05/10/35/40 Processor Handbook PDP-11 Peripherals Handbook | DEC-11-HKDBB-A-D<br>DEC-11-HMFMA-B-D<br>DEC-11-HBKEF-A-D<br>–<br>– |

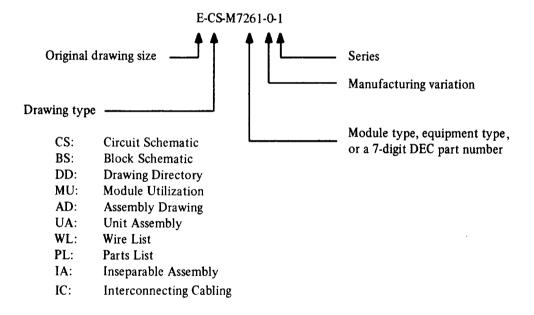

# 1.4 REFERENCE DRAWINGS

PDP-11/05/10-S systems are shipped with a set of engineering drawings for the basic components and applicable options. A list of the drawings is included in the Drawing Directory prints within each set.

DEC drawing numbers are interpreted as indicated in the following example:

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides information on PDP-11/05/10-S environmental and electrical requirements, equipment installation, and customer acceptance. The installation procedures contained in this chapter include installation of a basic PDP-11/05/10-S computer and a sample installation of an SCL interface compatible device — an LA36 DECwriter.

Installation procedures for the various available peripherals are provided in the maintenance manuals supplied with the peripherals.

# 2.2 ENVIRONMENTAL REQUIREMENTS

An ideal computer room type environment has an air distribution system that provides cool, well-filtered, humidified air. The room air pressure should be higher than that of adjacent areas to prevent dust infiltration.

#### 2.2.1 Humidity and Temperature

The PDP-11/05/10-S electronics are designed to operate in a temperature range from 41° F (5° C) to 122° F (50° C) at a relative humidity of 10 to 95 percent, without condensation. However, system configurations that use I/O devices, such as magnetic tape units, card readers, etc., require an operational temperature range of from 60° F (15° C) to 80° F (27° C) with 40 to 60 percent relative humidity. Nominal operating conditions for a system configuration are a temperature of 70° F (20° C) and a relative humidity of 45 percent.

# 2.2.2 Air Conditioning

When used, computer room air conditioning equipment should conform to the requirements of the "Standard for the Installation of Air Conditioning and Ventilating Systems (Non-residential)," N.F.P.A. No. 90A; as well as the requirements of the "Standard for Electronic Computer Systems," N.F.P.A. No. 75.

# 2.2.3 Special Mounting Conditions

If the PDP-11/05/10-S is to be subjected to rolling, pitching, or vibration of the mounting surface (e.g., aboard a ship), the cabinet in which the PDP-11/05/10-S is housed should be securely anchored to the installation floor by mounting bolts. Since such installations require modifications to system cabinets, Digital must be notified upon placement of the order so that necessary modifications can be made.

# 2.2.4 Static Electricity

Static electricity can be an annoyance to personnel and can, in extreme cases, affect the operational characteristics of the PDP-11/05/10-S Computer and related peripherals. If carpeting is installed on the installation room floor, it should be of a type designed to minimize static electricity. Flooring consisting of metal panels, or flooring with metal edges, should be adequately grounded.

# 2.3 ELECTRICAL REQUIREMENTS

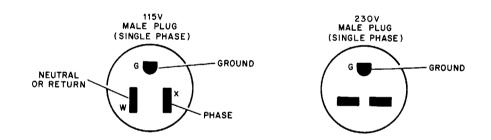

The PDP-11/05/10-S can be operated from a nominal 115 V, 50/60 Hz or 230 V, 50/60 Hz ac power source, depending on the type of ac input box installed in the mounting box power supply. The primary ac operational voltages should be maintained within the defined tolerances. Line voltage should be maintained within 90 Vac -132 Vac or 180 Vac -264 Vac, and the 50/60 Hz line frequency should not vary more than 3 Hz. The minimal configuration of the PDP-11/05/10-S computer (processor plus 16K of memory) requires approximately 575 VA of input power (5 A @ 115 Vac, 2.5 A @ 230 Vac).

Primary power outlets at the installation site must be compatible with the PDP-11/05/10-S primary power input connectors, or, if a 861 Power Controller is used, with the primary power input connectors of the power controller. The power receptacles must be provided by the customer.

The PDP-11/05/10-S uses only two types of connectors, depending on whether it is configured for 115 Vac or 230 Vac operation. The NEMA L5-15 connector is used for 115 Vac primary power; the L6-15 is used for 230 Vac primary power. Figure 2-1 shows the plug portion of each connector, indicates which equipment version uses it, and provides connector specifications.

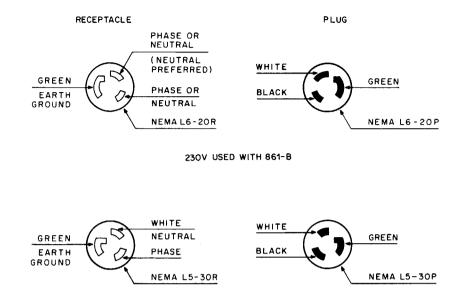

The 861 Power Controller, if used, requires power receptacles different from the PDP-11/05/10-S. The 861-C Power Controller, used for 115 Vac operation requires a NEMA L5-30 connector. The 861-B Power Controller, used for 230 Vac operation, requires a NEMA L6-20 connector. Figure 2-2 illustrates these connectors while Table 2-1 provides connector specifications.

CONNECTOR SPECIFICATIONS

| MODEL NUMBER    | NEMA* CONFIGURATION | DESCRIPTION  | POLES | WIRES | PLUG            |        | RECEPTACLE      |        |

|-----------------|---------------------|--------------|-------|-------|-----------------|--------|-----------------|--------|

|                 |                     |              |       |       | DEC<br>PART NO. | HUBBEL | DEC<br>PART NO. | HUBBEL |

| PDP-11/0S/10-SC | L5-15               | 115V, 15AMP  | 2     | 3     | 90-08938        | 5266-C | 12-05351        | 5262   |

| PDP-11/0S/10-SD | L6-15               | 230V, 15 AMP | 2     | 3     | 90-08853        | 5665-C | 12-11204        | 5662   |

<sup>\*</sup>ADD P SUFFIX FOR PLUG ADD R SUFFIX FOR RECEPTACLE

11 - 2568

Figure 2-1 PDP-11/05/10-S Connectors

Figure 2-2 861-B, C Power Controller Connectors

115V USED WITH 861-C

11-2438

Table 2-1

861-B, C Power Controller Primary Power Receptacles

| Model<br>Number | Power                 | Rating | Plug<br>NEMA CODE | Receptacle (Suppose NEMA CODE | olied by Customer) DEC Part No. |

|-----------------|-----------------------|--------|-------------------|-------------------------------|---------------------------------|

| 861-C           | 115 V<br>Single Phase | 30 A   | L5-30P            | L5-30R                        | 12-11191                        |

| 861-B           | 230 V<br>Single Phase | 20 A   | L6-20P            | L6-20R                        | 12-11194                        |

The PDP-11/05/10-S three-prong power connector, when inserted into a properly wired receptacle, should ground the computer chassis. It is unsafe to operate the computer unless the case is grounded because normal current leakage from the power supply flows to the metal parts of the chassis. If the integrity of the ground circuit is questionable, the user is advised to measure the potential between the computer case and a known ground with a voltmeter.

Computer systems are often sensitive to the interference present on some ac power lines. If the computer is to be installed in an electrically noisy environment, it may be necessary to condition the ac power line. Primary power to the computer should be provided on a line separate from lighting, air conditioning, etc., so that computer operation is not affected by voltage surges of fluctuations.

Any questions regarding power requirements and installation wiring should be directed to the Digital Sales engineer or Field Service engineer.

# 2.4 INSTALLATION PROCEDURES

The procedures presented in the following paragraphs are provided to assist in unpacking, inspecting, and installing the PDP-11/05/10-S Computer and associated SCL device.

#### CAUTION

Do not attempt to install the computer until Digital has been notified and a Digital Field Service representative is present.

# 2.4.1 Unpacking

The PDP-11/05/10-S is shipped ready to operate in a protective box. Prior to final electrical testing, each computer is thermal cycled and vibrated.

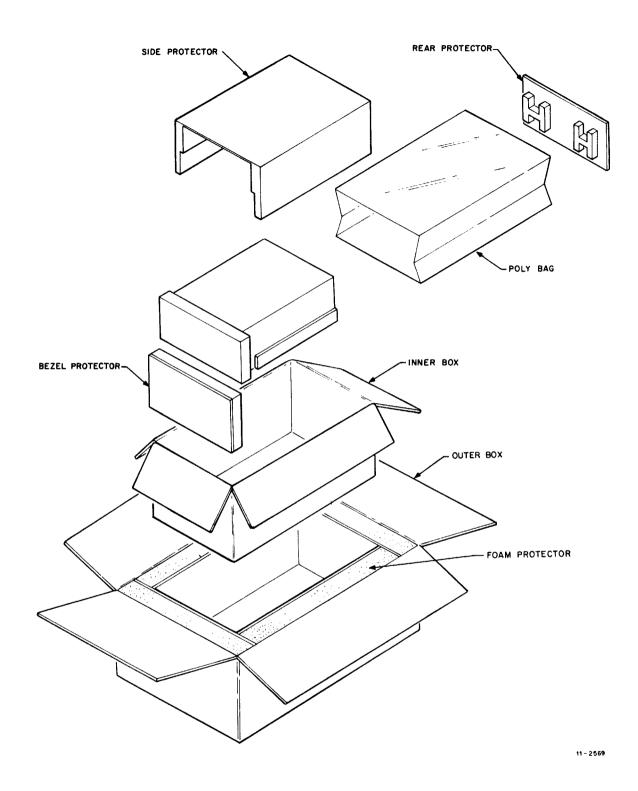

Basic computers are shipped in the package illustrated in Figure 2-3. Sufficient hardware is included in the shipping carton to rack mount the computer.

The PDP-11/05/10-S should be removed carefully from its box. Slide mounts are attached to the computer and mounting screws are packed in a bag in the same shipping carton. Also included is one Serial Communication Line (SCL) cable and two keys to the console power switch lock.

# 2.4.2 Inspection

After removing the computer from its carton, inspect it and report any damage to the local Digital Sales Office. Inspect as follows:

- 1. Inspect the box, bezel, switches, and indicators for damage.

- 2. Remove the top cover and inspect for loose or broken modules, blower or fan damage, cable damage, and loose nuts, bolts, screws, etc.

- 3. Remove the bottom cover and inspect wiring side of the logic panels for bent pins, broken wires, loose external components, and foreign material.

- 4. Inspect the power supply for proper seating of power connectors.

# 2.4.3 Cabinet and Slide Mounting Specifications

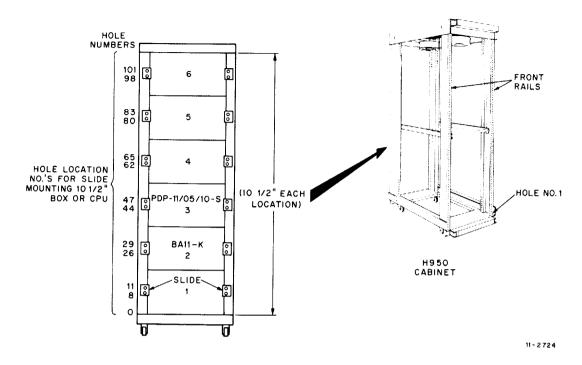

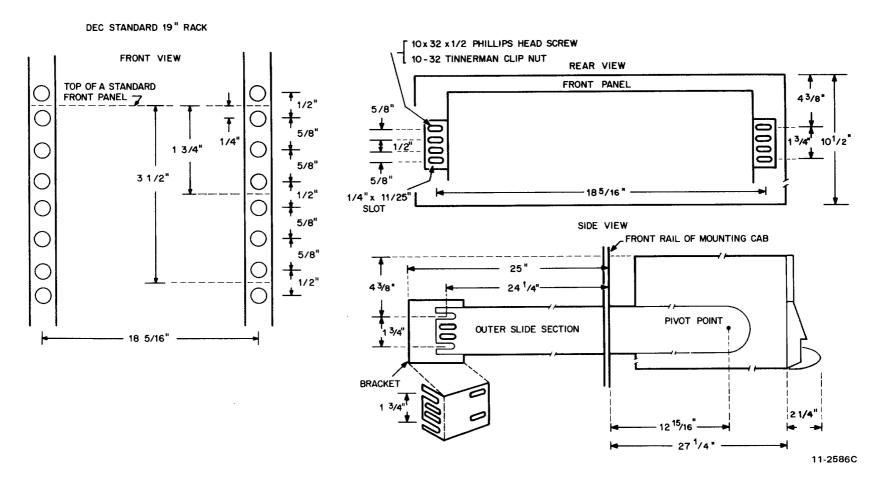

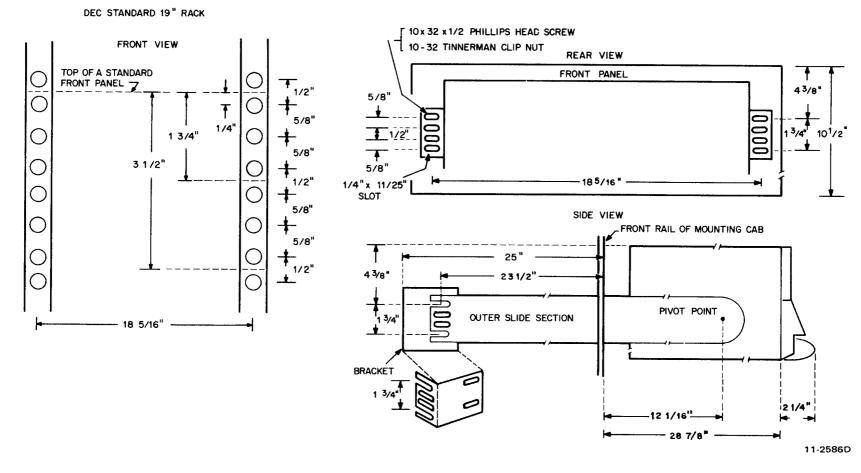

The PDP-11/05/10-S and a BA11-K can be mounted in an H950 cabinet. When using an H950 cabinet, the standard configuration is to place the PDP-11/05/10-S in location 3 and the BA11-K in location 2 (shown in Figure 2-4). The hole numbers shown on Figure 2-4 indicate the exact physical location for mounting an Accuride or Chassis-Trak slide on the front rail. Although the front rail slide placement is identical for both slides, there are some mounting differences when fastening the slides to a chassis. Figures 2-5 and 2-6 illustrate the specific slide mounting specifications for Accuride and Chassis-Trak, respectively.

Cabinet Power Control Option — Provisions have been made for the computer switch to operate an optional cabinet power control. This feature permits the programmer's console OFF/POWER/PANEL LOCK switch to control the power supply for peripherals connected to the computer. Operation of the programmer's console is explained in Chapter 3. For operating and wiring information on the power control option, refer to the maintenance manual provided with the option.

#### 2.4.4 Installation of LA36 DECwriter as an SCL Device

The LA36 is frequently used to connect to the PDP-11/05/10-S SCL interface. For a complete LA36 installation procedure, refer to the installation chapter of the LA36 DECwriter Service Manual, DEC-00-H36MM-A-D.

Figure 2-3 Computer Packaging

Figure 2-4 PDP-11/05/10-S and BA11-K Mounting Box Cabinet Mounting Specification

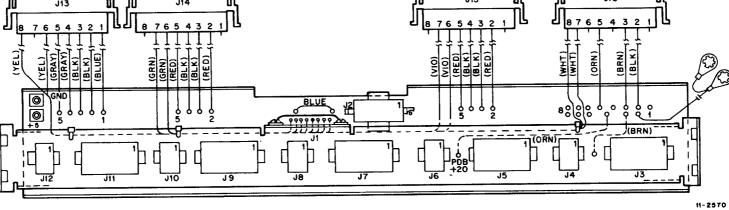

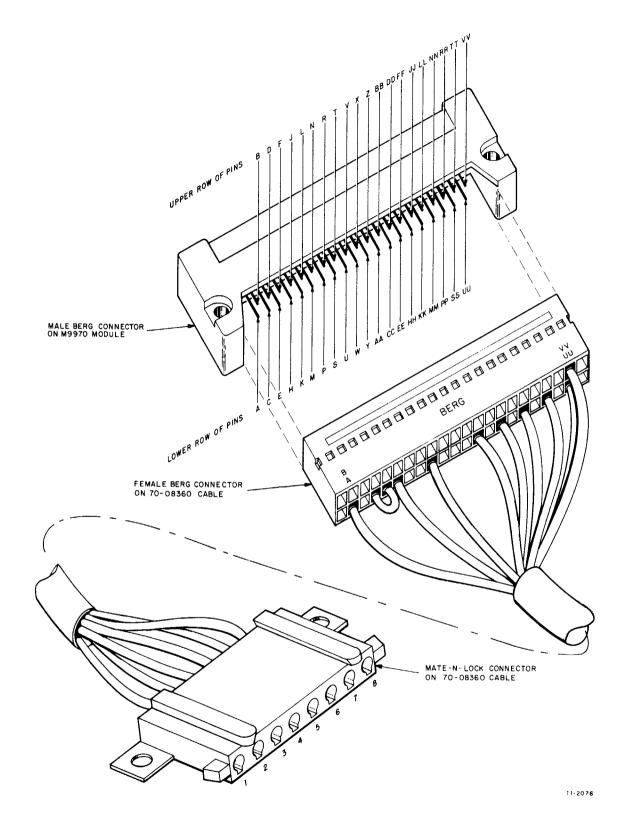

To connect the LA36 to the PDP-11/05/10-S SCL interface, route the LA36 serial interface cable to the PDP-11/05/10-S and connect to the Mate-N-Lok connector on the cable (No. 70-08360) hanging from the rear of the PDP-11/05/10-S.

If there is no cable hanging at the rear of the processor mounting box, remove the PDP-11/05/10-S top cover and then remove the M9970 connector module from backplane slots A4-B4. Plug the Berg connector on the 70-08360 SCL cable (supplied) into the Berg connector on the M9970. Insert the M9970 into backplane slots A4-B4. Run the SCL cable through the strain relief clamp of the PDP-11/05/10-S mounting box, and connect to the cable attached to the LA36.

Appendix A contains more detailed information on the SCL cable interconnections.

After initial power turn-on (Paragraph 2.4.5), perform the SCL baud rate adjustment check (Paragraph 7.4.2.3) to ensure that the SCL interface is set to 300 baud, the maximum transfer rate of the LA36 DECwriter.

Figure 2-5 Accuride Slide Mounting Specification

Figure 2-6 Chassis-Trak Slide Mounting Specification

# 2.4.5 Initial Power Turn-On

Before plugging in the computer ac power cord:

- 1. Ensure that the proper voltage (115 Vac or 230 Vac) is available at the wall receptacle.

- 2. Remove the computer mounting box bottom cover and disconnect the backplane power harness(es) from the power supply power distribution board.

- 3. Plug in the computer ac power cord and set the programmer's console key switch to POWER.

- 4. Observe that the two mounting box fans operate.

- 5. Verify that the correct voltages are present at the power distribution board connectors pins, as indicated in Table 2-2.

- 6. Set the console key switch to OFF, unplug the ac power cord, and reconnect the power harness(es) to the power distribution board.

- 7. Plug in the ac power cord and verify correct operation of the console OFF/POWER/PANEL LOCK key switch (Paragraph 3.2.1).

Table 2-2

No Load Voltage Verification

| Power Distribution Board<br>Connector J11 or J9<br>Pin Numbers (See Notes) | Voltage (Vdc) |

|----------------------------------------------------------------------------|---------------|

| 1, 4                                                                       | +5            |

| 2                                                                          | +15           |

| 3                                                                          | +20           |

| 5, 7, 8, 9, 11                                                             | GND           |

| 13                                                                         | -15           |

| 14                                                                         | -5            |

Note: Pins 6, 10, 12 and 15 are spares.

# 2.5 INSTALLATION CERTIFICATION

Once the computer has been installed, it is strongly recommended that a system diagnostic be run to ensure that the equipment operates correctly and that installation has been properly performed. Because system configurations vary widely, no one diagnostic will completely exercise all the attached devices.

The MAINDEC User's Manual that comes with the diagnostic package should be consulted for the appropriate diagnostic to be run, depending upon the attached devices. The MAINDEC User's Manual lists the devices that each diagnostic will exercise. The three system exercisers presently available are T17 System Exerciser (MAINDEC-11-DZQKB) for relatively small systems, General Test Program (MAINDEC-11-DZQGA) for medium to large systems, and Communications Test Program (MAINDEC-11-DZQCA) for communications-oriented systems. At least one of the above diagnostics and, if appropriate, the other two, should be used to verify system operation.

Once the diagnostic is selected, the respective diagnostic write-up should be consulted for specific operating instructions. If the user is not familiar with console operation and/or procedures for loading paper tapes, he should read Chapter 3 of this manual.

# CHAPTER 3 SYSTEM OPERATION

# 3.1 SCOPE

This chapter provides the information necessary to operate and program the PDP-11/05/10-S Computer. The description is divided into three major parts: programmer's console, basic system operation, and basic system programming. The description of controls and indicators for the console provides the user with the type and function of each operating switch and indicator. Operating controls for peripheral devices that are *not* part of the basic machine are contained in the appropriate peripheral manual.

Basic step-by-step procedures for both manual and program operation are given in Paragraph 3.5. Basic system programming is covered in Paragraph 3.6.

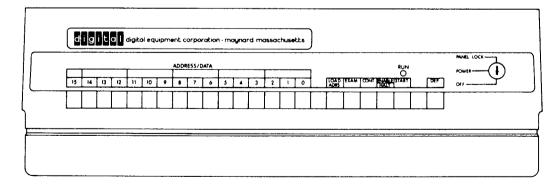

# 3.2 KY11-J PROGRAMMER'S CONSOLE

The KY11-J Programmer's Console (Figure 3-1) provides the PDP-11/05/10-S Computer with a necessary and useful programmer's interface. Manual operation of the computer is controlled by switches mounted on this console which is the front panel of the computer mounting box. Visual displays indicate processor operation and the contents of register and memory addresses.

All register switches and displays are ordered from right to left. The order corresponds to the exponential powers of two, i.e.,  $2^{15} \dots 2^2$ ,  $2^1$ ,  $2^0$ . Therefore, the most significant bit (MSB) is at the left of each specific register or display, the least significant bit (LSB) is at the right. Whenever an indicator is on, it denotes the presence of a binary 1 in the particular bit position. The alternate color coding on the console identifies the different functions or segments of the binary word in octal format. Figure 3-1 shows the location of all PDP-11/05/10-S console controls and indicators.

Figure 3-1 PDP-11/05/10-S Programmer's Console

# 3.2.1 Console Power Key Switch

The console power key switch has three positions:

OFF Fully counterclockwise

POWER 90° clockwise from OFF

PANEL LOCK 180° clockwise from OFF

In the OFF position, ac power is removed from the primary of the computer power supply. In the POWER position, ac power is applied to the computer power supply; the computer is fully operative. In the PANEL LOCK position, the computer is fully powered as in the POWER position. However, the console function switches (Paragraph 3.2.2) are disabled, thus protecting the computer against mischievous tampering during unattended program execution.

#### 3.2.2 Function Switches

Listed below in the order of their position (left to right) are the six switches on the right hand side of the console — the function switches:

- 1. LOAD ADRS (load address)

- 2. EXAM (examine)

- 3. CONT (continue)

- 4. ENABLE/HALT

- 5. START

- 6. DEP (deposit)

Function switches 1, 2, 3 and 5 (above) are spring loaded and return to their rest state when released; they are actuated by being depressed. The DEP switch is also spring loaded, but is actuated by being lifted. The ENABLE/HALT switch is a two position switch. Operation of the function switches is described in Paragraph 3.3.

# 3.2.3 ADDRESS/DATA Switches

The 16 ADDRESS/DATA switches are to the left of the function switches (Figure 3-1). These 2-position switches represent a manually set flip-flop register with the up position representing a logical 1 and the down position a logical 0. The ADDRESS/DATA switches may be used in conjunction with the function switches or in conjunction with a program stored in the computer's memory. The ADDRESS/DATA switches are often referred to as the Switch register in DEC documentation.

# 3.2.4 Console Indicators

There are seventeen indicators on the computer console: a RUN light and 16 ADDRESS/DATA lights. The RUN light, when lit, indicates that a program is being executed. The contents of the 16 ADDRESS/DATA lights either represent a 16-bit address, or the contents of a register or memory address. Table 3-1 indicates the meaning of the ADDRESS/DATA lights for all cases where the contents of these lights is defined. Note that the state of the ADDRESS/DATA lights is defined only when the computer RUN light is not illuminated.

#### 3.3 CONSOLE OPERATION

The following paragraphs describe the operation of the function switches.

Table 3-1 Significance of ADDRESS/DATA Indicators

| Action               | Qualification                                                                                                    | Information Displayed In ADDRESS/DATA Indicators                           |

|----------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Power On             | ENABLE/HALT switch in     HALT position                                                                          | 1. Contents of location (24) <sub>8</sub>                                  |

|                      | ENABLE/HALT switch in ENABLE position                                                                            | Undefined – depends on contents of memory                                  |

| Load Address         | LOAD ADRS switch depressed                                                                                       | Contents of Switch Register                                                |

| Examine              | 1. EXAM switch depressed                                                                                         | Unibus address that is to be examined                                      |

|                      | 2. EXAM switch released                                                                                          | Contents of Unibus address     that was examined                           |

| Deposit              | 1. DEP switch raised                                                                                             | Unibus address that is to be deposited                                     |

|                      | 2. DEP switch released                                                                                           | Contents of Switch Register which is the data deposited                    |

| RUN Light On         |                                                                                                                  | Undefined                                                                  |

| Program Halt         | 1. ENABLE/HALT switch in HALT position                                                                           | Address of instruction to     be executed when CONT     switch is actuated |

|                      | 2. HALT instruction executed                                                                                     | 2. Same as 1                                                               |

|                      | 3. Double bus error which is two successive attempts to access non-existent memory or improper odd byte address. | Contents of program     counter (R7) at time     double bus error occurred |

| Program<br>Execution | 1. START switch depressed                                                                                        | 1. Address of last load address                                            |

| Execution            | 2. CONT switch depressed                                                                                         | 2. Address of instruction to be executed                                   |

#### 3.3.1 Load Address Switch

Depressing the LOAD ADRS switch when the computer is halted causes the contents of the Switch Register to be stored in a temporary register within the computer. This data is also displayed in the ADDRESS/DATA lights for verification. The load address operation performs the following functions:

- Selects an address for a subsequent examine operation.

- Selects an address for a subsequent deposit operation.

- Selects the starting address of a program.

# 3.3.2 Examine Switch

The EXAM switch permits the display of the contents of a selected address in the ADDRESS/DATA lights. Select the appropriate address in the Switch Register and depress the LOAD ADRS switch. Then depress and release the EXAM switch. The contents of the selected address will then be displayed in the ADDRESS/DATA lights.

Several features are built into the examine function to aid in programming the computer:

- While the EXAM switch is depressed, the address to be examined is displayed. The data itself is displayed when the switch is released.

- If the EXAM switch is repeatedly depressed, the Unibus address is incremented by two on each depression\*. This permits the examination of a list of addresses without repeated load address operations.

- If an attempt is made to examine non-existent memory, it is necessary to perform the initialize operation explained in Paragraph 3.4.

- Only full words are displayed in the ADDRESS/DATA lights; thus, bit 0, the byte address bit, is ignored when using the EXAM switch with the following exception. Note that the general registers are located on byte addresses. Therefore, when examining the general registers, address bit 0 is recognized and the increment feature is modified so that sequential registers may be examined by repeated use of the EXAM switch.

The EXAM switch has no effect while the computer is in the RUN state or when the key operated power switch is in the PANEL LOCK position.

# 3.3.3 Deposit Switch

The physical operation of the DEP switch requires that it be lifted for actuation. The DEP switch permits the contents of the Switch Register to be deposited in a Unibus address, which is typically specified by a previous load address operation. To deposit the instruction BRANCH SELF (777<sub>8</sub>) in location 200<sub>8</sub>, first set the Switch Register to 200<sub>8</sub>, and then actuate the LOAD ADRS switch. Set the Switch Register to 777<sub>8</sub> then lift and release the DEP switch

Several additional features are built into the deposit function:

- While the DEP switch is actuated, the address to be effected is displayed in the ADDRESS/DATA lights. When the switch is released, the data deposited is displayed for verification.

- If the DEP switch is repeatedly depressed, the address is incremented by two on each depression\*\*. This permits depositing an entire program with only one load address operation.

<sup>\*</sup>The address is incremented by one when examining general registers.

<sup>\*\*</sup>The address is incremented by one when depositing into general registers.

- If an attempt is made to deposit into non-existent memory, it is necessary to perform the initialize operation explained in Paragraph 3.4.

- All deposit operations affect full 16-bit words. Bit 0 of the address is used only when depositing into general registers; otherwise, bit 0 of the address is ignored.

# 3.3.4 ENABLE/HALT Switch

Place the ENABLE/HALT switch in the HALT position; the computer will halt at the end of the current instruction providing the key switch is not in the PANEL LOCK position. All interrupts and traps will be executed prior to halting. This switch may be used in conjunction with the CONT switch to step through programs (Paragraph 3.3.6). With the ENABLE/HALT switch in the ENABLE position, programs may be executed, once started by actuating the START switch, actuating the CONT switch, and the auto-restart power-up sequence.

# 3.3.5 START Switch

To start a program from the console:

- 1. Set the starting address of the program in the Switch Register.

- 2. Depress the LOAD ADRS switch.

- 3. Position the ENABLE/HALT switch in the ENABLE position.

- 4. Depress and release the START switch.

While the START switch is depressed, the following actions occur:

- 1. An initialize signal is generated on the Unibus. This initialize signal serves to reset all peripherals.

- 2. The processor status word is reset to zero.

- 3. The program counter, R7, is loaded with the last address loaded with the LOAD ADRS switch.

When the START switch is released, program execution begins with the instruction contained in the location specified by R7 and the RUN light is turned on. If the ENABLE/HALT switch is in the HALT position, the computer remains in the HALT state following the release of the START switch.

Observe the following precautions when using the START switch:

- 1. If the key lock is not in the PANEL LOCK position, depressing the START switch while a program is running initializes the computer system and restarts the program.

- 2. It is good practice to precede every program start with a load address operation.

- 3. A program should not be started at an odd address or the first fetch operation will be aborted and an odd address trap will be attempted. If the stack pointer, R6, is not properly set up, the program in memory may be destroyed.

# 3.3.6 Continue Switch

The CONT switch is used to continue a program without altering the program counter, R7, or the machine state. To continue a halted program, depress and release the CONT switch. The program is resumed when the CONT switch is released.

The CONT switch is used with the ENABLE/HALT switch to step through programs one instruction at a time. If the CONT switch is actuated while the ENABLE/HALT switch is in the HALT position, a single instruction will be executed. Interrupts are serviced in single instruction mode. In single step mode, the address of the next instruction to be executed is displayed in the lights.

# 3.4 UNCONDITIONAL COMPUTER AND UNIBUS INITIALIZATION

Unconditional initialization of the computer system usually occurs because of an attempt to examine from, or deposit into, non-existent memory from the console. However, a peripheral or processor error may occur that can only be overcome by initializing the system from the console. The procedure is simply to depress the START switch with the ENABLE/HALT switch in the HALT position.

#### 3.5 BASIC OPERATION

Many methods exist for storing, modifying, and retrieving information from the PDP-11/05/10-S Computer. These methods depend on the form of the information, time limitations, and the peripheral equipment connected to the processor. The following procedures are basic to the use of the PDP-11/05/10-S Computer. Although they may be used less frequently as the programming and use of the system become more sophisticated, they are valuable in preparing the initial programs and in learning the function of system input and output transfers. For an understanding of the various operational controls and indicators, refer to Paragraph 3.3.

Operating procedures are separated into the following categories:

| Power on                  | Paragraph 3.5.1 |

|---------------------------|-----------------|

| Basic console control     | Paragraph 3.5.2 |

| Manual program loading    | Paragraph 3.5.3 |

| Automatic program loading | Paragraph 3.5.4 |

| Memory Dumps              | Paragraph 3.5.5 |

| Running programs          | Paragraph 3.5.6 |

#### 3.5.1 Power On

When the programmer's console OFF/POWER/LOCK switch is turned from OFF to POWER, the system is initialized (zeroed). A time delay allows sufficient time for voltages to logic units (especially memory elements) to stabilize.

The power-up initialization logic directly sets the microprogram control to a sequence of controlled events. If the console ENABLE/HALT switch is set to HALT when power is turned on, the processor microflow is directly set to the console microloop. The machine awaits the activation of a console control switch.

The LOCK position of the programmer's console OFF/POWER/LOCK switch provides for program operation with the console control switches disabled. However, the console Switch register may still be accessed.

# 3.5.2 Basic Console Control

Two major areas of control exist: control influenced by the ENABLE/HALT switch, which selects either program or console control; and control by the switches and sequences used for loading data manually into the processor.

3.5.2.1 ENABLE/HALT Switch – When the processor has control (ENABLE/HALT in ENABLE), either the START or CONT switch causes the program to run. The START switch initializes the system and begins operation at a specific address determined by the last console operation (usually LOAD ADRS). The CONT switch merely releases console control, and the program continues at the existing Program Counter (PC).

When the ENABLE/HALT switch is set to HALT, the console obtains control. The LOAD ADRS, EXAM, and DEP switches can be used. The CONT switch can now cause the processor to step through the program a single instruction at a time.

3.5.2.2 Loading Data Manually — Whenever data is manually loaded into a computer, it is desirable to have the address increment automatically upon each deposit. Thus, the user can set a starting address and continue to store data in sequential memory locations providing only new data for each location. The programmer's console logic also permits the user to immediately examine the data just deposited without re-addressing, to re-deposit if necessary,

and to continue with automatic incrementation. These sequences are associated with the functioning of the DEP and EXAM switches.

The address in the load address register does not increment the *first* time EXAM or DEP is used after a HALT or LOAD ADRS. It does not increment if DEP is used immediately after EXAM or if EXAM is used immediately after DEP. It does increment if a DEP is used immediately after a DEP, or if an EXAM is used immediately after an EXAM. This increment is a word increment as the console is word oriented. Thus, the user can look at a location, change it, deposit the changed data, and then reexamine it without having to load an address each time.

Incrementation is on even boundaries for all addresses except the addresses specifically designated for the processor internal registers, which are incremented by 1.

For example, to alter several successive locations, the following steps are performed:

- 1. LOAD ADRS (starting location)

- 2. EXAM (no increment looks at starting location)

- 3. DEP (no increment loads starting location)

- 4. EXAM (no increment checks previous deposit)

- 5. EXAM (increment looks at next location)

- 6. DEP (no increment loads second location)

- 7. EXAM (no increment checks previous deposit)

- 8. EXAM (increment looks at third location)

If the user wants to take advantage of automatic address incrementation for examining or loading data, the following steps can be used to load data into sequential locations:

- 1. LOAD ADRS (starting location)

- 2. DEP (no increment loads starting location)

- 3. DEP (increment loads second location)

- 4. DEP (increment loads third location)

- 5. DEP (increment loads fourth location) etc.

The same procedure can be used for examining data in sequential memory locations.

# 3.5.3 Manual Program Loading (Bootstrap Loader)

A primary manual use of the programmer's console is to store the bootstrap loader in the core memory. (Programs and data can be stored or modified by manual use of the programmer's console.) The bootstrap loader (DEC-11-L1PA-LA) is a minimal instruction program that can automatically load programs into core memory from a paper tape punched in a special bootstrap format. One of these programs, after being stored, can in turn, load any binary format tape into the computer. (An explanation of the number designations used for DEC programs is given in Table 3-2.)

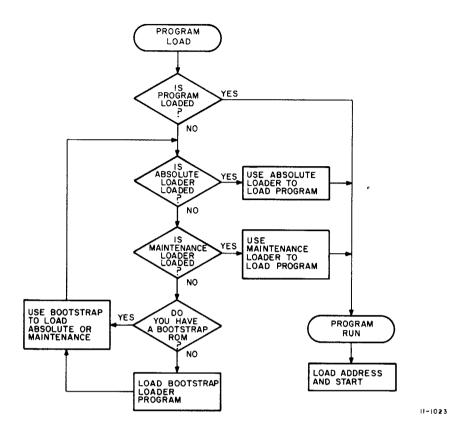

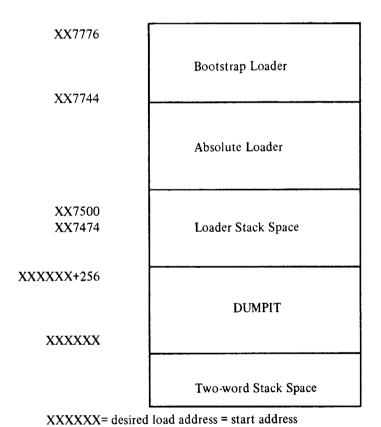

The sequence for loading the computer is shown in Figure 3-2, with programs noted as follows:

**Bootstrap loader** (DEC-11-L1PA-LA) — manually loaded by console switches; provides for automatic loading of programs punched in a special format.

Absolute loader – punched in special format; loaded by bootstrap loader; provides for automatic loading of programs punched in binary format.

Selected program - punched in binary format; loaded automatically by absolute loader.

Table 3-2 Program Identification Codes

| Format:  | COMPUTER<br>PRODUCT<br>DEC-1                        | IDENTIFICATION  DISTRIBUTION  -LIPA-LA                                                                                                                                                                       |

|----------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Notes:   | 1 2                                                 | <b>4 4 4 4</b> 4 4 3 4 5 6 7 8                                                                                                                                                                               |

| 1        | Product Code                                        | MAINDEC = maintenance library products DEC = programming library products                                                                                                                                    |

| 2        | Computer Series                                     | 11 = PDP-11 Computer Systems                                                                                                                                                                                 |

| 3        | Major Category                                      | L = Loader                                                                                                                                                                                                   |

| 4        | Minor Category (sequential numbers)                 | 1 = first in a series of programs<br>2 = second in series, etc.                                                                                                                                              |

| 5        | Option Category (hardware required to use software) | P = paper tape system H = high-speed reader and/or punch K = Teletype keyboard only M = magtape                                                                                                              |

| 6        | Revision Category (sequential letters)              | A = basic program B = first revision C = second revision, etc.                                                                                                                                               |

| 7        | Distribution Method                                 | L = listing P = paper tape                                                                                                                                                                                   |

| 8        | Distribution Mode                                   | A = ASCII B = binary (absolute) O = other (bootstrap binary)                                                                                                                                                 |

| Example: | DEC-11-L2PB-PO                                      | Indicates a PDP-11 programming library product, second in a series of loaders, requiring a paper tape system to use, the first revision to the program, supplied as a paper tape in bootstrap binary format. |

To eliminate the necessity of more than one bootstrap loader, the bootstrap loader instructions contain two variables (x and y) to provide compatibility with various memory configurations and reading devices. These variables are listed in Table 3-3. A complete explanation of the bootstrap loader program is given in the *Paper Tape Software Programming Handbook* (DEC-11-XPTSA-A-D); further information may be found in the program listing, DEC-11-L1PA-LA.

Figure 3-2 Flowchart of Procedure for Loading and Running Programs

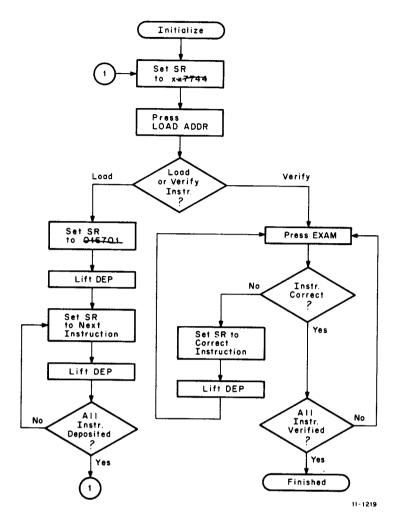

The following procedure (illustrated in flowchart form in Figure 3-3) is used to manually load the bootstrap loader program (DEC-11-L1PA-LA):

- 1. Set ENABLE/HALT switch to HALT to give bus control to the console when powering up.

- 2. Turn OFF/POWER/LOCK switch to POWER position. This energizes the programmer's console.

- 3. Enter starting address of bootstrap loader (Table 3-3) into Switch register. Make certain that the correct xx value is used (077744 for 16K memory, 137744 for 24K memory, etc.).

- 4. Depress LOAD ADRS switch. The address set in the Switch register is shown on the ADDRESS display.

- 5. Enter starting address contents (016701) into Switch register.

- 6. Lift DEP switch. The contents just entered in the Switch register is displayed in the DATA display.

- 7. Enter contents of next address into Switch register.

# NOTE

It is not necessary to load addresses after the starting address has been loaded because the address is automatically incremented by two each time DEP is used consecutively.

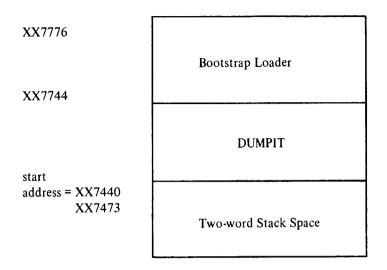

Table 3-3 Bootstrap Loader (DEC-11-L1PA-LA)

The bootstrap loader should be toggled into the highest core memory bank.

| Address | Instruction |

|---------|-------------|

| xx7744  | 016701      |

| xx7746  | 000026      |

| xx7750  | 012702      |

| xx7752  | 000352      |

| xx7754  | 005211      |

| xx7756  | 105711      |

| xx7760  | 100376      |

| xx7762  | 116162      |

| xx7764  | 000002      |

| xx7766  | xx7400      |

| xx7770  | 005267      |

| xx7772  | 177756      |

| xx7774  | 000765      |

| xx7776  | уууууу      |

xx represents highest available memory bank. First location of the loader is one of the following, depending on memory size: xx in all subsequent locations is the same as the first.

| Address | Memory Size |

|---------|-------------|

| 077744  | 16K         |

| 137744  | 24K         |

| 157744  | 28K         |

Contents of address xx7776 (yyyyyy) should contain device status register address of paper-tape reader to be used when loading the bootstrap formatted tape. Addresses are: