# A Simple 2708 EPROM Programmer for the Motorola D2 Kit

Add 2K of firmware using a handful of components that fit right on the D2 board.

Frank W. Summers Motorola Microsystems 514 E. Carmen St. Tempe AZ 85283

Add up to 2K bytes of programmable memory to your Motorola MEK6800-D2 kit with this simple, low-cost 2708 EPROM programmer. Requiring only three transistors, six resistors, four capacitors and two switches, it can be assembled right on the D2 kit printed circuit board for approximately \$7.

The reason for using the 2708type EPROM is simple—its cost. The newer, larger, single supply EPROMs are too expensive for most home computer users. The 2708 type (with its + 5 V, + 12 V and -5 V requirement) is available to the hobby user for less than \$10. The fact that the D2 kit has two EPROM sockets available for 2708s makes this a natural matchup. Just think, you can buy a D2 kit and add this programmer for less than the cost of many programmers alone!

Don't worry about investing in an expensive ultraviolet

EPROM eraser, because most local computer stores offer this service for a small fee. If this isn't convenient, you can build an EPROM eraser for less than \$20 using a germicidal lamp (G.E. #G8T5) and a suitable fixture. If you try this be sure to follow the precautions that come with the lamp about exposure to ultraviolet radiation.

## **Circuit Description**

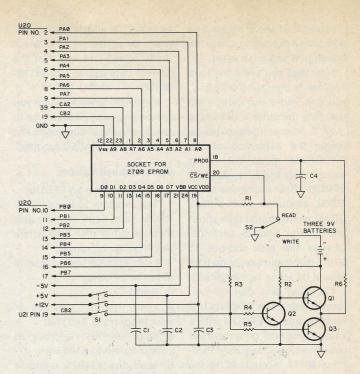

Only a brief description of the circuit is offered because it is simple. The +27 V for the programming pulse is supplied

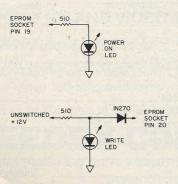

Fig. 1. Optional LEDs to indicate Power On and Write mode.

from three 9 V batteries connected in series. Since the current required from these batteries is only 20 mA and only during the actual programming of a device, the shelf life of the batteries will probably determine their usage. The power switch (S1) will remove the +5 V and +12 V from the EPROM socket and disconnect CB2 of PIA U21. When the EPROM socket is empty and S1 is off, there is nothing connected to the PIAs so they can be used for other applications.

The read/write switch (S2) applies ground to pin 20 (CS/WE) and removes the ground from the +27 V source when in the read position. When in the write position pin 20 (CS/WE) is pulled up to +12 V through a 10k resistor (R1) and the ground is applied to the +27 V source. This allows programming pulses to be applied to pin 18 (PROG) through transistor Q1 as controlled by CB2 of the PIA (U21 of the D2 kit).

The two 100 Ohm resistors (R4 & R5) balance the base drive to Q2 and Q3. The 10 Ohm resis-

tor (R6) and the .005 uF capacitor (C4) limit the rise-and-fall time of the +27 V programming pulse to the EPROM. All data to and from the EPROM is through the B side of the user PIA (U20 of the D2 kit). The addressing for the EPROM is from the A side of the user PIA (U20 of the D2 kit), plus CA2 and CB2 for address lines A8 and A9, respectively.

# **Programming**

The software to operate the programmer requires 375 bytes of memory and supplies these four functions:

- 1. PROGRAM—programs the EPROM from the memory locations specified.

- 2. VERIFY—compares the EPROM with the memory locations specified.

- 3. DOWNLOAD—copies the EPROM into the RAM locations specified.

- ERASED?—checks that the specified EPROM locations are erased.

The only inputs required for all of these operations are: (1) starting memory address, (2) ending memory address and (3) EPROM address offset. Once these parameters are entered they will remain the same until changed by the user.

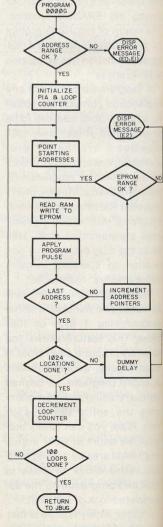

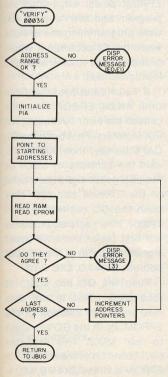

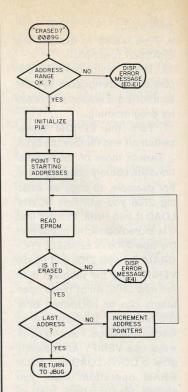

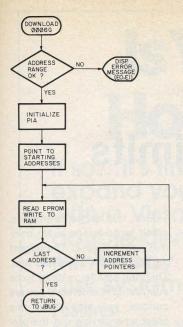

When any function is started these addresses are checked for proper range. The function is stopped and error message E0 is displayed if the difference between the ending and starting address is greater than 1024. If adding the EPROM offset to this difference exceeds 1024, error message E1 is displayed; error message E2 indicates that the EPROM address tried to exceed 1024 while the program function was executing.

Obviously this should never happen unless the programmer program itself bombs. Error message E3 indicates that the EPROM and specified memory locations didn't agree during the VERIFY function. Error message E4 indicates an unerased location was found in the specified EPROM locations during the ERASED function. The return of the JBUG prompt "-" to the display means the designated function has completed with no errors.

A programming pulse of one millisecond duration is applied for each EPROM address to be programmed. If less than 1024 locations are being programmed, enough delay is added to simulate programming the entire device. This routine is repeated 100 times to give each location a total of 100 milliseconds programming time. This limits the duty cycle of any one location as specified in most manufacturers' data books.

The programming time will be about two minutes whether programming 1 byte or 1024 bytes. This feature allows you to safely program an EPROM in short blocks, adding routines or entire programs as desired without erasing and reprogramming the entire device each time. Also, you can safely program the entire EPROM from a small RAM area by putting each successive block of code in RAM and programming the appropriate block of EPROM.

Another safety feature is that the D2 kit's keyboard is disabled while programming to avoid the possibility of the escape key being pressed and leaving the +27 V applied to the EPROM.

The delay routine is for a system clock frequency of 614.4 kHz. If your system has a different clock frequency, the number of counts in the delay loop will have to be adjusted accordingly. (Change location \$00A9 to \$A6 for 1 MHz.)

### **Test Procedure**

So now you have the 2708 programmer circuit added to your D-2 kit and the software typed in. Before you do anything else you should save the program on tape. That done, you can use the following test procedure to verify the circuit and the program before plugging an EPROM into the socket. All you will need is a VOM, a watch with a second hand and a 2708 EPROM.

First check that the -5 V is on pin 21 of the EPROM socket. Then check for the +12 V on pin 19 and +5 V on pin 24 . . . make sure they are switchable with S1. Pin 20 should have +12 V when the read/write switch is on write and 0 V when in the read position. To check the +27 V on pin 18 the program will have to be temporarily changed. Change location \$0035 from \$8D to \$3E. This is the WAI (wait for interrupt) instruction and will stop program execution at this point.

With the power switch on and the read/write switch set to write, the voltage on pin 18 should be 0 V. Referring to the operating instructions, start the PROGRAM mode with the first, last and EPROM offset addresses set to \$0000. The voltage on pin 18 should now be between + 25 V and + 27 V. Switch back to read, and the voltage on pin 18 should drop to 0 V. Hit reset, restore location \$0035 to \$8D and turn the power switch

Now you will need some known data patterns to write to the EPROM socket for verification. Starting at location \$0178 store \$FF, \$00, \$55 and \$AA. Set the first address to \$0178 and the last address to \$017B. You are now set up to simulate

Fig. 2. Schematic of 2708 EPROM programmer for D2 kit.

programming these four bytes to the first four locations of the **FPROM**

Set a breakpoint at \$0030 and start the PROGRAM mode. All address lines of the EPROM socket should now read a logical 0 level (less than 0.5 V). All data lines should read a logical 1 level (more than 3.0 V). Continue program execution to the breakpoint again by typing E then G. Now address line A0 should read a 1 level; A1 through A9 should read a 0 level; and the data lines should all read a 0 level. Type E and G again and you should read a 1 level on A1, a 0 level on all other address pins, and the data lines should be alternate 1s and 0s (D0 = 1, D1 = 0, etc.).

Continue once more to the breakpoint and the results should be: A0 and A1 at a 1, all other address lines at 0, and the data lines alternate 0s and 1s (D0 = 0, D1 = 1, etc.). That's it for the data lines. Hit E, set the EPROM address offset to \$0155 and start the PROGRAM mode again. The address lines at the EPROM socket should now be alternate 1s and 0s (A0 = 1,A1 = 0, etc.). Push E, set the EPROM address offset to \$02AA and start the PROGRAM mode again. The address lines should now be alternate 0s and 1s (A0 = 0, A1 = 1, etc.). Clear the breakpoint and hit reset.

You can make a check of the loop counter by setting a breakpoint at \$0068 and executing the PROGRAM mode. Now push the E key and the G key 100 times. This should cause the "-" to appear on the display in-

2N4401 or equivalent Q1, Q2, Q3 3PST toggle switch Sı SPDT toggle switch S2 C1, C2, C3 .1 uF, ±20% ceramic capacitor .005 mfd, ± 20% ceramic capacitor C4 R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> 10k Ohm, ± 10% 1/4 Watt carbon resistor 100 Ohm, ± 10% 1/4 Watt carbon resistor R4, R5 10 Ohm, ± 10% 1/4 Watt carbon resistor R MISC. 24-pin socket for EPROM, three 9 V batteries, battery clips and battery holders.

dicating that the program has completed executing. Clear the breakpoint and push reset.

Now that you know the loop counter is operating correctly, you can verify the delay loop that sets the pulse width of the +27 V programming pulse by timing the execution of the PROGRAM mode with your watch. With the first, last and EPROM offset addresses set at \$0000, execution of the PRO-GRAM mode should take about one minute and 25 seconds. Change the last address to \$03FF (1024) and execution time should be about two minutes.

The next text can be performed using the DOWNLOAD function and an EPROM with a known program or an erased one. First clear memory locations \$0177 through \$017F by storing \$00 to each location. Set the first address to \$0179 and the last address to \$017C. Plug the EPROM in, turn power on and execute the DOWN-LOAD function.

When the "-" returns to the display, read locations \$0177 through \$017F. Locations \$0179-\$017C should contain the first four bytes of the program in the EPROM (\$FF if erased). Locations \$0177, \$0178, \$017D, \$017E and \$017F should still contain \$00. Now run the VERI-FY function without changing anything, and the "-" should return indicating that EPROM and RAM contents for those four locations match. If you

00003

00005

00007 00008

00010 00011

00013 00013

00016 00017 00018

00019 00020

00022

00023 00024

00026 00027

have a 2708 with a known program, try a different EPROM address offset and see that the correct data appears in \$0179-

If everything works so far you are on your way. It is left up to you to try illegal addresses and to check the ERASED function.

### **Operating Instructions**

- A. To program an EPROM:

- 1. The program to be put in E-PROM must be in memory at a location other than that where the PG2708 program is.

- 2. Load PG2708 from cassette (if not in EPROM).

- 3. Reset.

- 4. Load the first address of your program at \$A032-3.

- 5. Load the last address of your program at \$A034-5.

- 6. Load the EPROM address offset \$A036-7.

- 7. Make sure the EPROM power switch is off and the Read/Write switch is on read.

- 8. Plug the 2708 into the programmer socket.

- 9. Turn the EPROM power switch on.

- 10. Turn the Read/Write switch to write.

- 11. Type 0000G to execute the PROGRAM function.

- 12. When the "-" returns to the display, push Reset and then turn the Read/Write switch to read.

- 13. Type 0003G to VERIFY that the EPROM was programmed correctly.

- 14. Turn the EPROM power

- switch off and remove the 2708.

- B. To download an EPROM to RAM.

- 1. Load PG2708 from cassette (if not in EPROM).

- 2. Reset.

- 3. Load the first RAM address at \$A032-3

- 4. Load the last RAM address at \$A034-5.

- 5. Load the EPROM address offset at \$A036-7.

- 6. Make sure the EPROM power switch is off and the Read/Write switch is on read.

- 7. Plug the 2708 into the programmer socket.

- 8. Turn the EPROM power switch on.

- 9. Type 0006G to execute the DOWNLOAD function.

- 10. Turn the EPROM power switch off and remove the 2708.

- C. To verify that EPROM and memory agree:

- 1. Load PG2708 from cassette (if not in EPROM).

- 2. Reset.

- 3. Load the first memory address at \$A032-3.

- 4. Load the last memory address at \$A034-5.

- 5. Load the EPROM address offset at \$A036-7.

- 6. Make sure the EPROM power switch is off and the Read/Write switch is on read.

- 7. Plug the 2708 into the programmer socket.

- 8. Turn the EPROM power switch on.

- 9. Type 0003G to execute the VERIFY function.

- 10. The "-" returns to the dis-

- play if the EPROM and memory agree

- 11. Turn the EPROM power switch off and remove the 2708.

- D. To check that a designated section of the EPROM is erased.

- 1. Load PG2708 from cassette (if not in EPROM).

- 2. Reset.

- 3. Load a first\* memory address at \$A032-3.

- 4. Load a last\* memory address at \$A034-5.

- \*(These can be any block of memory-they are used only to determine how many EPROM locations to check.)

- 5. Load the EPROM address offset at \$A036-7.

- 6. Make sure the EPROM power switch is off and the Read/Write switch is on read.

- 7. Plug the 2708 into the programmer socket.

- 8. Turn the EPROM power

Fig. 3. PROGRAM mode flowchart.

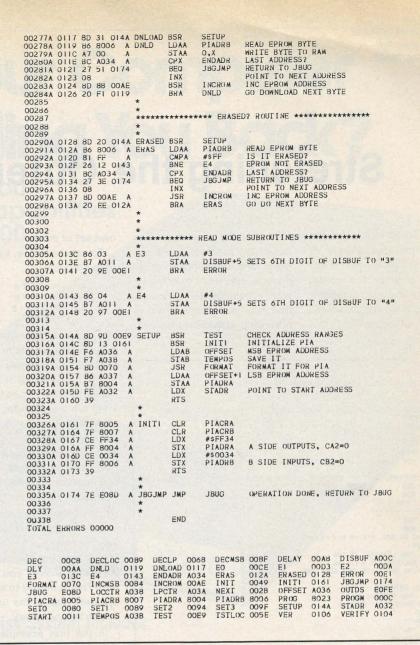

Program listing. 00001 00002A 0000 MCM2708 EPROM PROGRAMMER FOR D-2 \* REV. 2.2 \*\*\*\* MCM2708 EPROM PROGRAMMER BY FRANK SUMMERS \*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* NO FUNCTIONAL CHANGES THIS REVISION. CORRECTED LOCATION COUNTER INITIALIZATION. THIS ROUTINE WILL PROGRAM THE MOTOROLA MCM2708, MCM68708, OR MOST OTHER 2708 TYPE EPROMS ON A MOTOROLA MEK6800U-2 SINGLE BOARD COMPUTER (D2 KIT) 375 BYTES OF MEMORY IS REQUIRED FOR THIS PROGRAM. THE SIMPLE EPROM PROGRAMMER CIRCUIT (ATTACHED) CAN BE ASSEMBLED ON THE D-2 KIT PCB OR CAN BUILT SEPARATELY AND CONNECTED WITH A CABLE. NOTE THAT THE 2708 REQUIRES +5V, +12V, & -5V. THE +27V PROGRAMMING PULSE IS SUPPLIED BY THREE 9V BATTERIES. 100 27V PULSES OF ONE MSEC DURATION ARE APPLIED FOR EACH EPROM ADDRESS TO BE PROGRAMMED. \* THE KEYBOARD IS DISABLED TO PREVENT ACCIDENTALLY \* HITTING "ESCAPE" & LEAVING THE +27V APPLIED.

switch on.

- 9. Type 0009G to execute the ERASED? function.

- 10. The "-" returns to the display if the designated EPROM locations are erased and ready for programming.

- 11. Turn the EPROM power switch off and remove the 2708.

Two or more of these functions are usually used together. For example, to copy an existing 2708 you will first DOWN-LOAD it into RAM, VERIFY that it is stored correctly, check that the new 2708 is ERASED, PRO-GRAM the new 2708 and finally VERIFY that the program is in the new 2708. All of these operations can be performed after the address information is loaded only once. You should always use VERIFY immediately after a DOWNLOAD or a PRO-GRAM operation. Also, you should always check that an EPROM is ERASED before trying to PROGRAM it. (Even new EPROMs are not always erased!)

# **Error Messages**

If E0 or E1 appears on the display (indicating out of range addresses), check the first, last and offset addresses at \$A032-\$A037. E0 means the last address minus the first address is

Fig. 4. VERIFY mode flowchart.

| 00033                                                                                             |                   | *            |                   |                             |                                                                                  |

|---------------------------------------------------------------------------------------------------|-------------------|--------------|-------------------|-----------------------------|----------------------------------------------------------------------------------|

| 00034<br>00035                                                                                    |                   | * ENOUGH     | H DELAY           | IS ADDED                    | TO KEEP THE DUTY CYCLE                                                           |

| 00036<br>00037                                                                                    |                   | *            |                   |                             | PROGRAMMED.                                                                      |

| 00038<br>00039<br>00040                                                                           |                   | *            |                   |                             | ROGRAMS THE EPROM FROM RAM.                                                      |

| 00041<br>00042                                                                                    |                   | *            |                   |                             | RIFIES THAT EPROM & RAM AGREE.                                                   |

| 00043<br>00044                                                                                    |                   | *            |                   |                             | READS EPROM INTO RAM.                                                            |

| 00045<br>00046                                                                                    |                   | *<br>* 4. ER | ASED (\$          | 0009) VEH                   | RIFIES THAT EPROM IS ERASED.                                                     |

| 00047<br>00049                                                                                    |                   | *            | *** ()PE          | RATING IN                   | STRUCTIONS *******                                                               |

| 00050<br>00051                                                                                    |                   | * CAUII      | ON! THE           | READ/WRI                    | TE SWITCH SHOULD BE LEFT IN<br>EPT WHEN ACTUALLY PROGRAMMING                     |

| 00052<br>00053<br>00054                                                                           |                   | * AN EPI     | ROM. LE           | AVING IN                    | WRITE WILL DISCHARGE BATTERIES.                                                  |

| 00055<br>00056                                                                                    |                   | * 1. LO.     | AD STAR           | TING HAM                    | ADDRESS AT \$A032-3.                                                             |

| 00057<br>00058                                                                                    |                   | *            |                   |                             | RESS AT \$A034-5.                                                                |

| 00059<br>00060                                                                                    |                   | *            |                   |                             | OFFSET AT \$A036-7.                                                              |

| 00061<br>00062<br>00063                                                                           |                   | *            |                   |                             | TE FOR PROGRAMMING ONLY!                                                         |

| 00064<br>00065                                                                                    |                   | *            |                   |                             | SSES BEFORE PROGRAMMING!                                                         |

| 00066                                                                                             |                   |              |                   |                             |                                                                                  |

| 00068<br>00069                                                                                    |                   | *<br>* 8. TH | E JBUG            | PROMPT WI                   | ILL RETURN WHEN FINISHED.                                                        |

| 00070 * (PROGRAMMING TAKES 1.5 TO 2 MINUTES) 00071 *                                              |                   |              |                   |                             |                                                                                  |

| 00072                                                                                             |                   |              |                   |                             |                                                                                  |

| 000/4 ******** ERROR MESSAGES ************************************                                |                   |              |                   |                             |                                                                                  |

| 000/6                                                                                             |                   |              |                   |                             |                                                                                  |

| 000/9                                                                                             |                   |              |                   |                             |                                                                                  |

| 00081 * (SELECTED FUNCTION NOT ATTEMPTED) 00082 * E2 = EPROW ADDRESS OVERRANGE WHILE PROGRAMMING. |                   |              |                   |                             |                                                                                  |

| 00084 * (SELECTED FUNCTION ABORTED WHEN OVERRANGE OCCURRED)                                       |                   |              |                   |                             |                                                                                  |

| 00085                                                                                             |                   |              |                   |                             |                                                                                  |

| 00038<br>00089                                                                                    |                   | * E4 =       | DESIGNA           | TED EPRO                    | M LOCATIONS NOT ERASED.                                                          |

| 00091<br>00092                                                                                    |                   | *            | *****             | ** EQUATE                   | S *******                                                                        |

| 00093<br>00094                                                                                    |                   | *<br>PIADRA  |                   | \$8004                      | LSB OF EPROM ADDRESS                                                             |

| 00096                                                                                             | 8006 A            | PIACRA       | EQU               | \$8005<br>\$8006            | CA2 = EPROM ADDRESS LINE A8 DATA TO & FROM EPROM                                 |

| 00098                                                                                             | 8023 A            |              | EQU<br>EQU        | \$8007<br>\$8023<br>\$E08D  | CB2 = EPROM ADDRESS LINE A9 CB2 = +27V PROGRAM PULSE CONTROL. JBUG REENTRY POINT |

| 00100                                                                                             | EOFE A            |              | EQU               | \$EOFE<br>\$AOOC            | JBUG DISPLAY ROUTINE JBUG DISPLAY BUFFER                                         |

| 00102<br>00103                                                                                    | A032 A            |              | EOU               | \$A032<br>\$A034            | START ADDRESS<br>END ADDRESS                                                     |

| 00104<br>00105                                                                                    | A038 A            | LOCCIR       | EQU               | \$A036<br>\$A038            | EPROM ADDRESS OFFSET LOCATION COUNTER                                            |

| 00106<br>00107                                                                                    |                   | TEMPOS       | EOU               | \$A03A<br>\$A03B            | LOOP COUNTER TEMPORY STORAGE FOR OFFSET                                          |

| 00108<br>00109<br>00110                                                                           |                   | *            | *****             | ** JUMP                     | TABLE **********                                                                 |

| 00111A 0000 7E<br>00112A 0003 7E                                                                  |                   |              | JMP<br>JMP        | PROGM<br>VERIFY             | PROGRAM MODE VERIFY MODE                                                         |

| 00113A 0006 /E<br>00114A 0009 /E                                                                  | 0117 A            |              | JMP JMP           | DNLOAD<br>ERASED            | DOWNLOAD MODE<br>ERASED? MODE                                                    |

| 00115<br>00116                                                                                    |                   | *            |                   | NEW PARTY                   |                                                                                  |

| 00117 ********* PROGRAM ROUTINE ************************************                              |                   |              |                   |                             |                                                                                  |

| 00119<br>00120A 000C BD<br>00121A 000F BD                                                         |                   |              | JSR<br>BSR        | TEST                        | CHECK ADDRESS RANGES INITIALIZE PIA                                              |

| 00122A 0011 8E<br>00123A 0014 F6                                                                  | A 810A            | START        | LDS<br>LDAB       | #\$AO78<br>OFFSET           | RESTORE STACK POINTER MSB EPROM ADDRESS                                          |

| 00124A 0017 F7<br>00125A 001A 8D                                                                  | A03B A<br>54 0070 |              | STAB<br>BSR       | TEMPOS<br>FORMAT            | SAVE IT<br>FORMAT IT FOR PIA                                                     |

| 00126A 001C B6<br>00127A 001F B7                                                                  | 8004 A            |              | LDAA              | PIADRA                      | LSB EPROM ADDRESS                                                                |

| 00128A 0022 CE<br>00129A 0025 FF<br>00130A 0028 FE                                                | A038 A            |              | LDX<br>STX<br>LDX | #\$400<br>LOCCIR<br>STADR   | SETS LOCATION COUNTER = 1024<br>POINT TO START ADDRESS                           |

| 00131A 0028 A6<br>00132A 002D B7                                                                  | 00 A              | NEXI         | LDAA<br>STAA      | O.X<br>PIADRB               | READ RAM BYTE WRITE BYTE TO EPROM                                                |

| 00133A 0030 86<br>00134A 0032 B7                                                                  | 34 A              |              | LDAA<br>STAA      | #\$34<br>PROG               | APPLY 27V PULSE, NMI DISABLED                                                    |

| 00135A 0035 8D<br>00136A 0037 86                                                                  | 71 00A8<br>3C A   |              | BSR<br>LDAA       | DELAY<br>#\$3C              | ONE MSEC DELAY                                                                   |

| 00137A 0039 B7<br>00138A 003C BC                                                                  | A034 A            |              | STAA<br>CPX       | PROG<br>ENDADR              | REMOVE 27V PULSE, NMI DISABLED LAST ADDRESS?                                     |

| 00139A 003F 27<br>00140A 0041 08                                                                  |                   |              | INX               | INCROM                      | CHECK LOCATION COUNTER POINT TO NEXT ADDRESS INC EPROM ADDRESS                   |

| 00141A 0042 8D<br>00142A 0044 BD<br>00143A 0047 20                                                | OOB9 A            |              | JSR<br>BRA        | DECLOC<br>NEXT              | DEC LOCATION COUNTER GO DO NEXT ADDRESS                                          |

| 00144                                                                                             | 5525              | *            |                   |                             |                                                                                  |

| 00147<br>00148                                                                                    | 0000              | *            |                   |                             | SUBROUTINES ******                                                               |

| 00149A 0049 7F<br>00150A 004C 7F<br>00151A 004F CE                                                | 8007 A            |              | CLR<br>CLR<br>LDX | PIACRA<br>PIACRB<br>#\$FF34 |                                                                                  |

|                                                                                                   | 8004 A            |              | STX               | PIADRA                      | A SIDE OUTPUTS, CA2=0<br>B SIDE OUTPUTS, CB2=0                                   |

| 00154A 0058 86<br>00155A 005A B7                                                                  | 64 A              |              | LDAA<br>STAA      | #\$64<br>LPCTR              | SETS LOOP COUNTER = 100                                                          |

|                                                                                                   |                   |              |                   |                             |                                                                                  |

```

00156A 005D 39

00157

HTS

00158

00159A 005E 7D A038

TEST LOCATION COUNTER (MSB)

ISI

LOCCIR

A TSTLOC

00160A 0061 26 65 00C8

00161A 0063 7D A039 A

00162A 0066 26 60 00C8

BNE

LOCCTR+1 TEST LOCATION COUNTER (LSB)

DEC

LPCIR DEC LOOP COUNTER

00163A 0068 7A A03A A DECLP

00164A 006B 26 A4 0011

00165A 006D 7E E08D A

DEC

START

JBUG

IF NOT LAST LOOP - START OVER

DONE - BACK TO JBUG

00166

00168A 0070 F6 A03B

GET EPROM ADDRESS (MSB)

A FORMAT

LDAB

00169A 0073 27 0B 0080

00170A 0075 5A

BFO

SETO

00171A 0075 5A

00171A 0076 27 11 0089

00172A 0078 5A

00173A 0079 27 19 0094

SFT1

BEQ

DECB

SET2

00174A 007B 5A

00175A 007C 27 21 0094

00175A 007C 27 21 0096

00176A 007E 20 5A 00UA

00177A 0080 C6 34 A

00178A 0082 F7 8005 A

00179A 0085 F7 8007 A

00180A 0088 39

DECB

SET3

BFQ

IF EPROM MSB GREATER THAN 3

SETS EPROM MSB = 0

BRA

LDAB

STAB

E2

#$34

PIACR

SETO

STAB

PIACRB

RTS

LDAB

00181A 0089 C6 3C

00182A 008B F7 8005

00183A 008E C6 34

00184A 0090 F7 8007

A SETI

SETS EPROM MSB = 1

STAB

PIACRA

LDAB

00185A 0093 39

00186A 0094 C6 34

00187A 0096 F7 8005

RTS

SET2

LDAB

#$34

PIACRA

SFTS FPROM MSB = 2

STAB

00188A 0098 F7 8007

00188A 0099 C6 3C

00189A 0098 F7 8007

00191A 009F C6 3C

00192A 00AI F7 8005

00193A 00A4 F7 8007

LDAB

PIACRB

STAB

SET3

LDAB

#$3C

SETS EPROM MSB = 3

STAB

STAB

RTS

PIACRA

PIACRB

00194A 00A/ 39

00195

00196

A DELAY

SETS ONE MSEC DELAY

LDAA

00197A 00A8 86 66

#$66

00198A 00AA 4A

00199A 00AB 26 FD 00AA

00200A 00AD 39

DECA

DLY

BNE

DLY

RTS

00201

00204A 00AE 7C 8004 A INCROM INC

00205A 00B1 27 01 00B4 BEQ

00206A 00B3 39 RTS

00207A 00B4 7C A03B A INCMSB INC

PIADRA

INC EPROM LSB

INCMSB

TEMPOS

INC EPROM MSB

00208A 00B7 20 B7 0070

00209

00210

BRA

FORMAT

LOCCTR+1 DEC LOCATION COUNTER (LSB)

DECMSB

LOCCTR

DECLP

LOCCTR

DEC LOCATION COUNTER (MSB)

00218

00219

00220A 00C8 8D EF 00B9 DEC

BSR

DECLOC

00221A 00CA 8D DC 00A8

00222A 00CC 20 90 005E

00223

DUMMY DELAY IF < 1024 BYTES

BSH

DELAY

BRA

TSTLOC

LAST LOCATION DONE YET?

00224

00225A 00CE 7F A011 A

00226A 00D1 20 0E 00E1

DISBUF+5 SETS 6TH DIGIT OF DISBUF TO "O" ERROR

CLR

00227

00228

00229A 00D3 86 01 A

00230A 00D5 B7 A011 A

00231A 00D8 20 07 00E1

DISBUF+5 SETS 6TH DIGIT OF DISBUF TO "I"

STAA

BRA

00233

00234A 00DA 86 02 A

00235A 00DC B7 A011 A

00236A 00DF 20 00 00E1

A E2

LDAA

DISBUF+5 SEIS 6TH DIGIT OF DISBUF TO "2"

BRA

ERROR

00237

00239A 00E1 86 0E

00240A 00E3 B7 A010

00241A 00E6 7E E0FE

00242

A ERROR

A

LDAA

DISBUF+4 SETS 5TH DIGIT OF DISBUF TO "E"

OUTDS EXIT & DISPLAY ERROR MESSAGE

STAA

00243

00244A 00E9 B6 A035 A

00245A 00EC F6 A034 A

00246A 00EF B0 A033 A

00247A 00F2 F2 A032 A

00248A 00F5 C1 04 A

00249A 00F7 24 D5 00CE

00250A 00F9 BB A037 A

00251A 00FC F9 A036 A

00252A 00FF C1 04 A

00253A 0101 24 D0 00D3

00243

TEST

LDAA

ENDADR+1

LDAB

ENDADR

SUBA

STADR+1

STADR

#4

E0

SBCB

OUT OF EPROM RANGE

BCC

ADD A

OFFSET+1

OFFSET

#4

ADCB

CMPB

BCC

EI

OUT OF EPROM RANGE

00254A 0103 39

00255

00256

00258

00259

************** VERIFY ROUTINE *********

00261

00262

00263A 0104 8D 44 014A VERIFY

00264A 0106 A6 00 A VER

00265A 0108 B1 8006 A

00266A 0108 26 2F 013C

00267A 0100 BC A034 A

00268A 0110 27 62 0174

00269A 0112 08

00270A 0113 8D 99 00AE

SETUP

READ RAM BYTE

COMPARE WITH EPROM BYTE

MEMORY & EPROM DON'T AGREE

LAST ADDRESS?

RETURN TO JBUG

LDAA

O,X

PIADRB

CMPA

BNE

E3

ENDADR

BEQ

JBGJMP

INX

POINT TO NEXT ADDRESS

INC EPROM ADDRESS

INCROM

BSR

00271A 0115 20 EF 0106

00272

BRA

VER

GO READ NEXT BYTE

00273

00274

******* DOWN OAD ROUTINE *******

00276

```

Fig. 5. ERASED? mode flow-chart.

greater than 1024, and E1 means the last address minus the first address plus the EPROM address offset is greater than 1024.

If E2 appears on the display the EPROM address tried to exceed 1024 while the program was executing. You should hit reset, switch to READ, switch EPROM power off, reload the program and start over. If you were programming the EPROM when the E2 occurred it would probably have to be erased and reprogrammed.

If E3 or E4 appears you can find which EPROM location caused the error by reading the PIA registers. First push the ESCAPE (E) key, then 8004M. Record the contents of \$8004 as the LSB (least significant byte) of the EPROM address. Now push the GO (G) key to read \$8005. This register indicates the first bit of the MSB (most significant byte) of the EPROM address (\$X4 = 0, \$XC = 1).

Push the GO key again to read \$8006. This is the data read from this location of the EPROM. Push the GO key again to read \$8007. This indicates the second bit of the MSB of the EPROM address (\$X4 = 0, \$XC = 1). Use this bit with the one

Fig. 6. DOWNLOAD mode flowchart.

from \$8005 to decode the MSB of the EPROM address. If both bits are 0 then the MSB = \$00; if the first bit is 1 and the second is 0 then the MSB = 1; if the first bit is 0 and the second is 1 then the MSB = \$02; and if both bits are 1 then the MSB = \$03.

If the error is E4 you now know which location is not erased and the contents of that location (an erased location reads \$FF), but about all you can do is to try erasing the EPROM again. If the error is E3 you can also read the corresponding RAM location to determine the difference between the EPROM and the RAM. If the difference is a bit in the EPROM that is a 1 and should be a 0, try programming it again. If it is a bit that is a 0 and should be a 1, the EPROM will have to be erased before programming.

If E3 errors continue to occur check your batteries for at least 8.5 volts each with a 20 mA load. Because the program stops execution when an error occurs, only the first error can be located in either case.

Don't let all these error messages scare you. With careful planning and keypunching you may never see one.

# **Final Thoughts**

A few notes about what types of programs to put in EPROM and how to modify them if nec-

essary to get you started: First, this program itself is an ideal candidate if you have limited RAM available because it will leave your entire RAM area free for the program that you are putting in EPROM. Other likely candidates to consider are: memory tests (so you can test all of your RAM), subroutines that you use frequently (saves RAM every time they are called), added functions that your monitor ROM doesn't perform and any other programs that you want ready to run immediately when your system is powered up.

Before putting a program in EPROM, you must first make sure it has no self-modifying code and that all jumps to absolute addresses within the program are changed to match what the addresses will be when the EPROM is plugged into its normal socket. No self-modifying code means all variables must be located in RAM somewhere else. In the D2 kit you can use the scratchpad RAM (\$A000-\$A07F) used by the monitor if you don't interfere with the monitor's variables. Generally \$A032-\$A05F can be used safely as is the case with this program, which uses \$A032-\$A03B.

There are eight jumps to absolute addresses within the program used with the 2708 EPROM programmer. Four of these are in the jump table at the beginning of the program. The others are located at lines 120, 142, 297 and 319. All of these must be changed to put this program in EPROM or to relocate anywhere else in RAM.

The 2708 EPROM programmer circuit was held to the minimum to keep the cost down. If you didn't mind spending a little more, it could be built into a separate box and connected to the D2 kit through connector J1. The +27 V could be supplied from a separate power supply if available. LEDs could be added to indicate when power was on and when the read/ write switch was in the write position (see Fig. 1). If you anticipate heavy use, a more expensive zero-insertion-force type socket should be used for the EPROM.